http://dustbunny.physics.indiana.edu/~paul/hallDrd

## GlueX (Jefferson Lab Hall D) Electronics R&D

## Indiana University Light Quark Physics Group

Paul Smith Indiana University, Department of Physics, Bloomington, IN, 47405

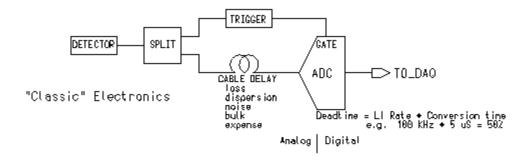

For the Jefferson lab GlueX experiment, we will be developing pipelined Flash ADC front end electronics. Traditionally, particle physics experiments delay detector signals in long coaxial cables to allow time for a trigger to be formed:

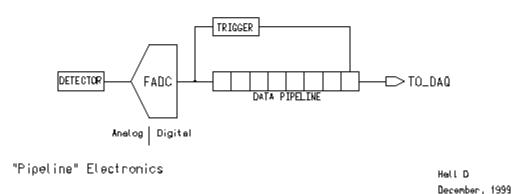

The pipeline approach continuously digitizes the detector data and stores the digital information. In parallel, the trigger uses the digital information to find interesting events. When the trigger condition is satisfied, time-delayed information is extracted from the pipeline for further processing by the data acquisition system.

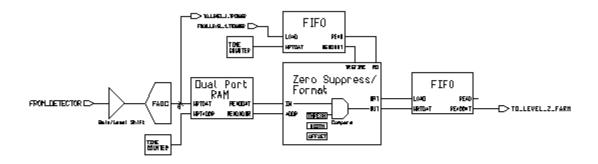

The pipeline can be implemented with Dual Port Random Acess Memory:

Flash ADC Data Pipeline

The FADC data is continuously written into the Dual Port RAM. Upon receipt of a level 1 trigger, the data from the associated time slice is read from the other port. This scheme introduces no deadtime since new data continue to be written while the old data is read.

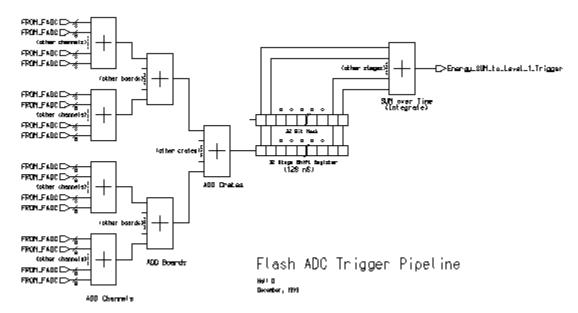

The FADC data is also used to form the level 1 trigger. A tree of adders sums information from the various channels in a detector system:

Within the next few years, this hardware will be prototyped at IU. Since the Hall D detector will require 10,000+ channels of this electronics, optimizing the cost is extremely important.

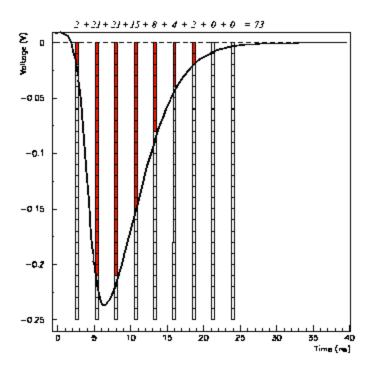

Flash ADCs are specified in terms of samples per second and number of bits of resolution. The individual samples can be added together to calculate the charge contained in a pulse:

## Pulse Digitization

Our goal is to optimize the resolution at which the pulses are digitized by varying the sampling frequency and the sampling depth.

The sampling depth is related to the smallest voltage change to which the device is sensitive. A depth of n bits will provide  $2^n$  divisions on the voltage scale

The sampling frequency is the rate at which the pulse is sampled. For shorter pulses higher frequencies are necessary.

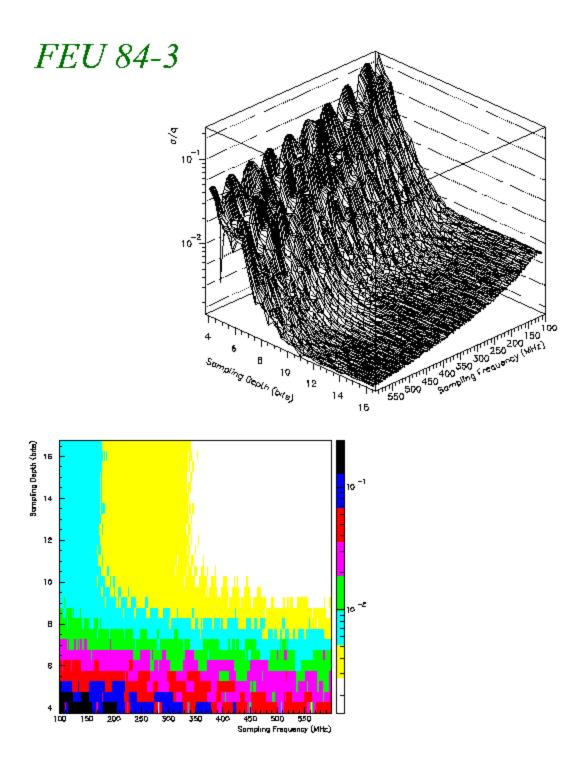

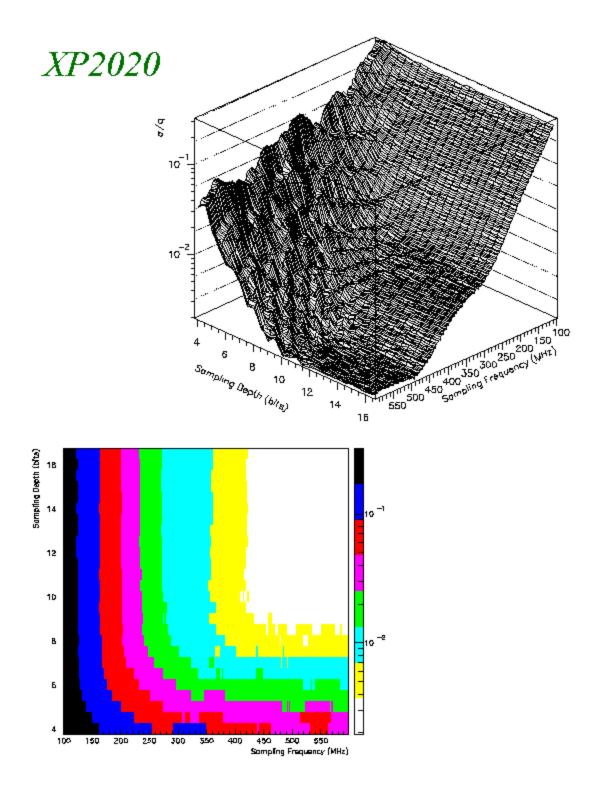

We varied the sampling rate and bit depth for simulated pulses from a slow photomultiplier (FEU84) and a fast photomultiplier (XP2020). The variance in the charge measurement divided by the measured charge is plotted:

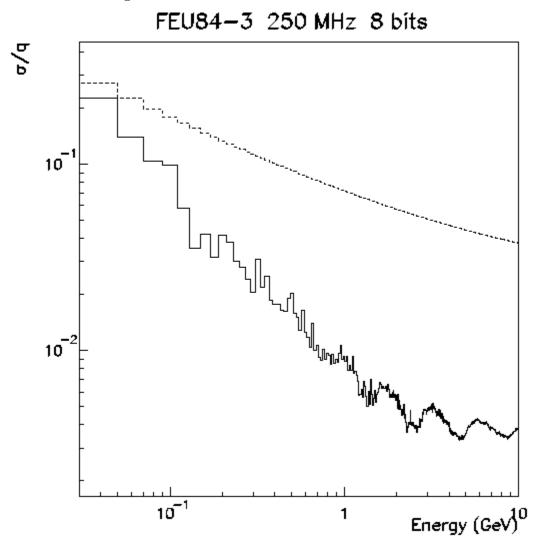

For the FEU84-3, summing the FADC samples results in an energy resolution better than the intrinsic

resolution of lead glass:

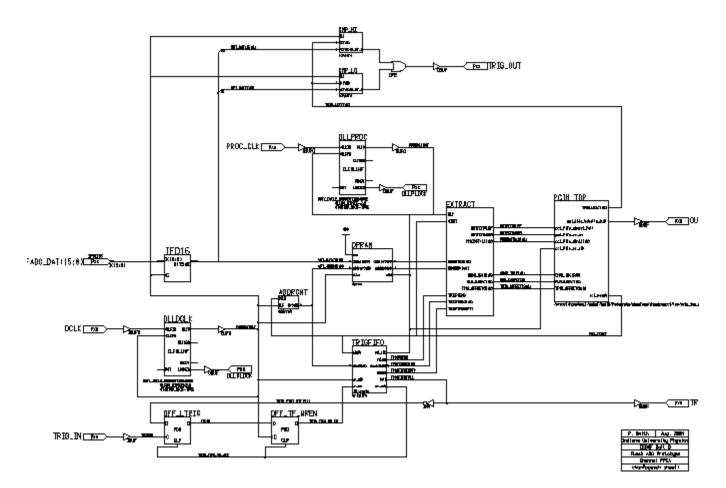

A Xilinx XC2S50 gate array which implements the dual port RAM buffering, feature extraction, and an interface to the PCI bus has been designed and simulated. Here is a block diagram:

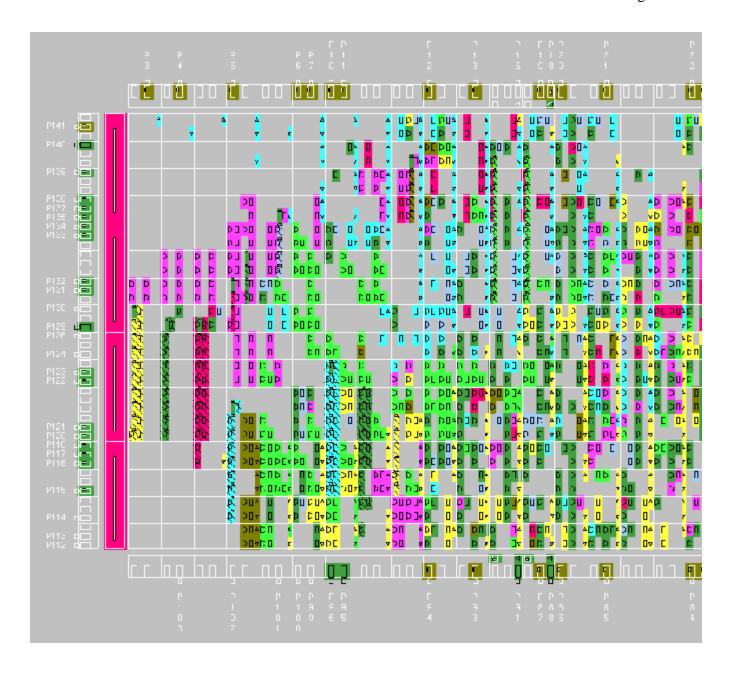

Here is a "floorplan" of the gate array:

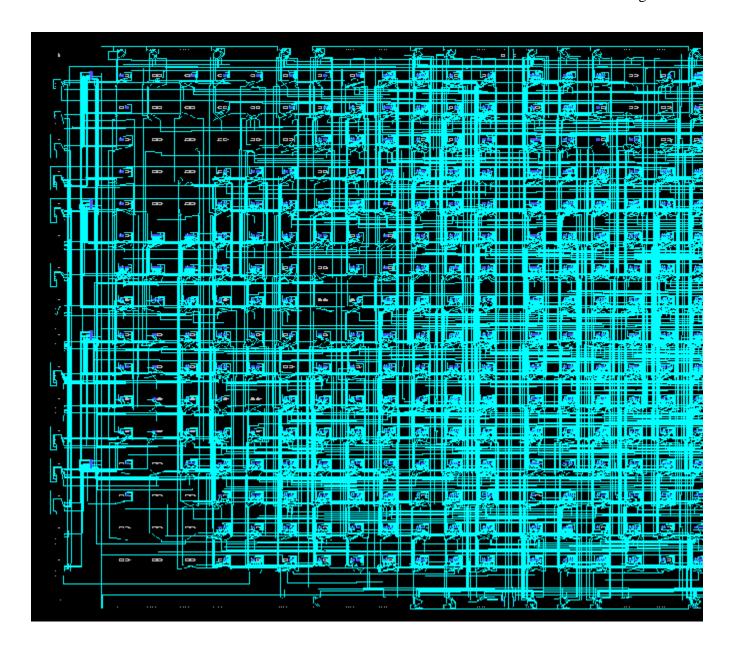

Here is the routing for the gate array:

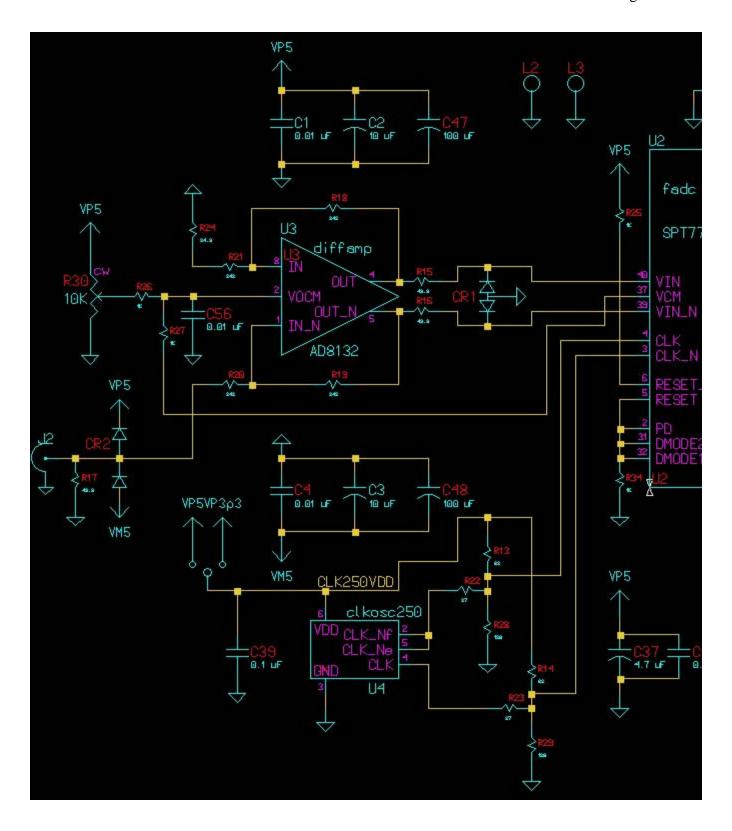

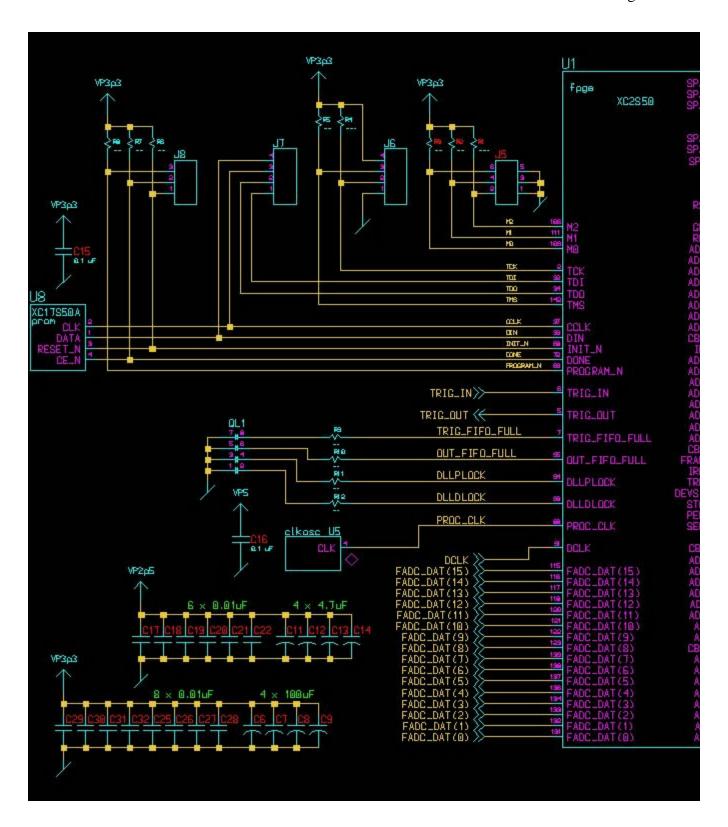

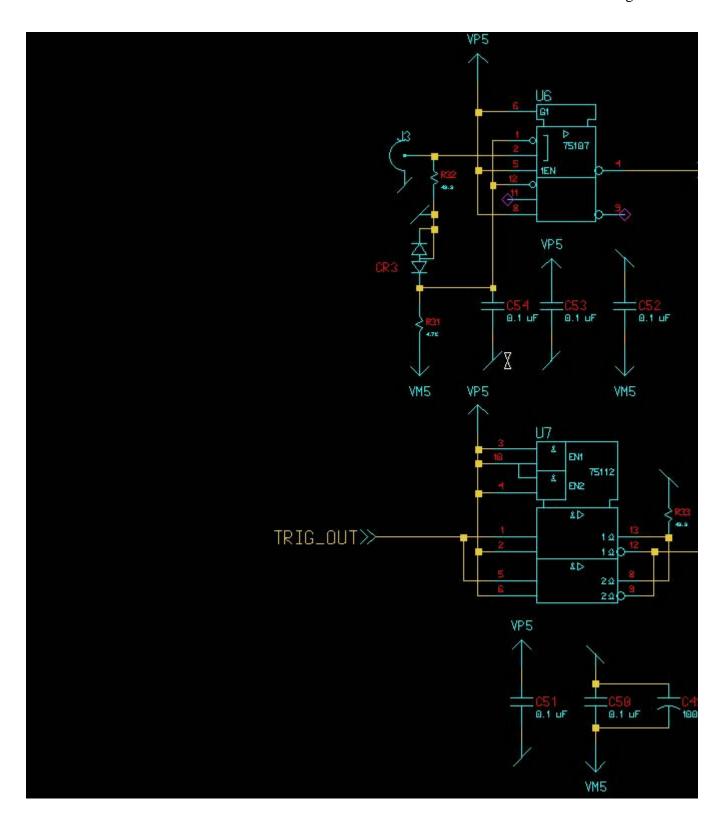

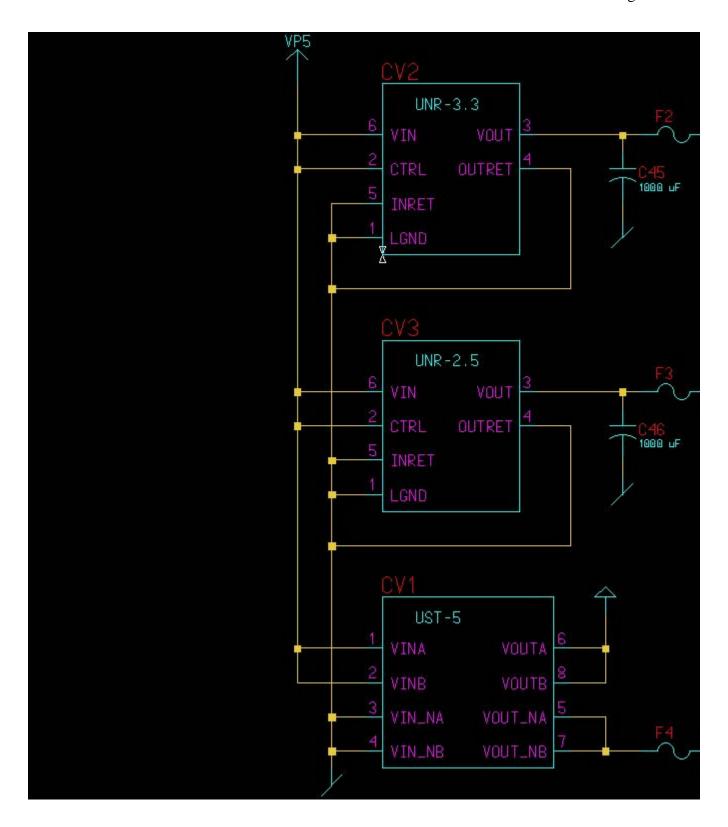

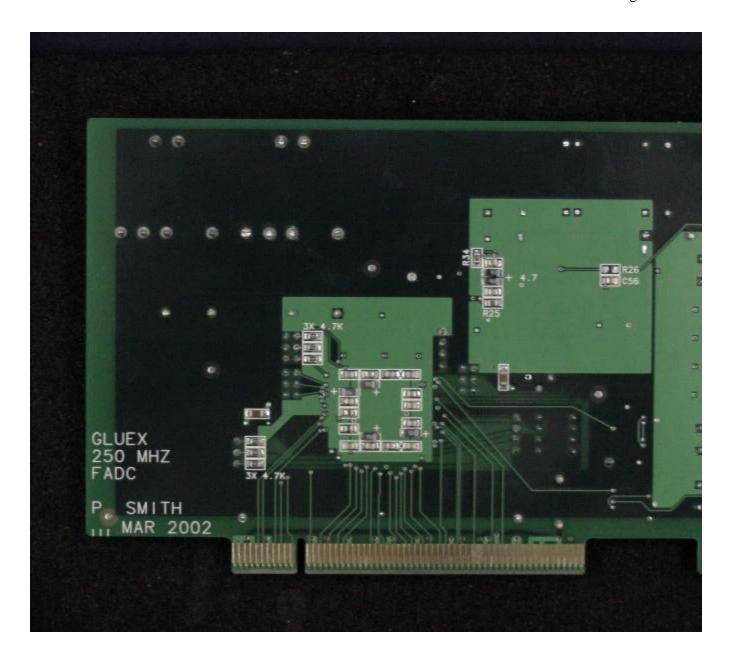

Here are schematics of a PCI card to test the FADC and Xilinx gate array:

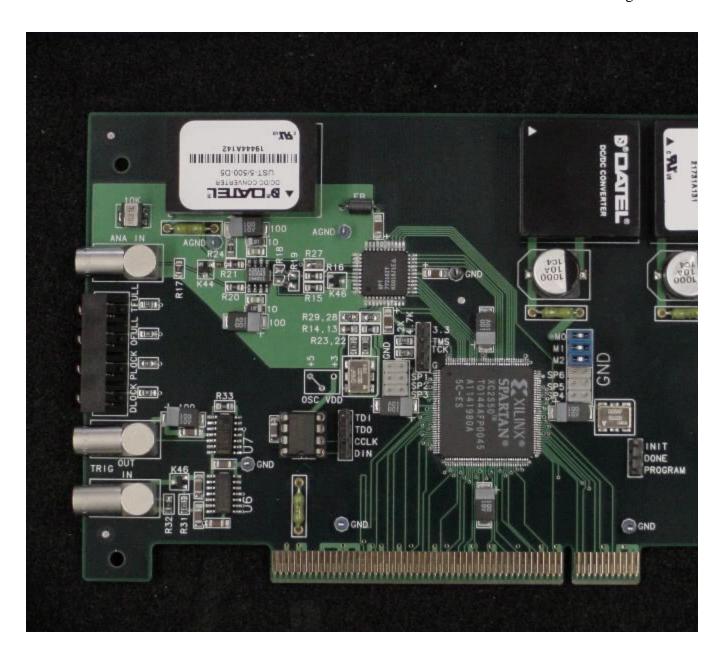

Here is the printed circuit:

Higher resolution and printable versions of the figures are available <u>here.</u> Sample waveforms are available <u>here.</u>

Register assignments and programming information is available <u>here</u>. Linux driver software is available <u>here</u>.

More information about the GlueX experiment is available <u>here</u>.