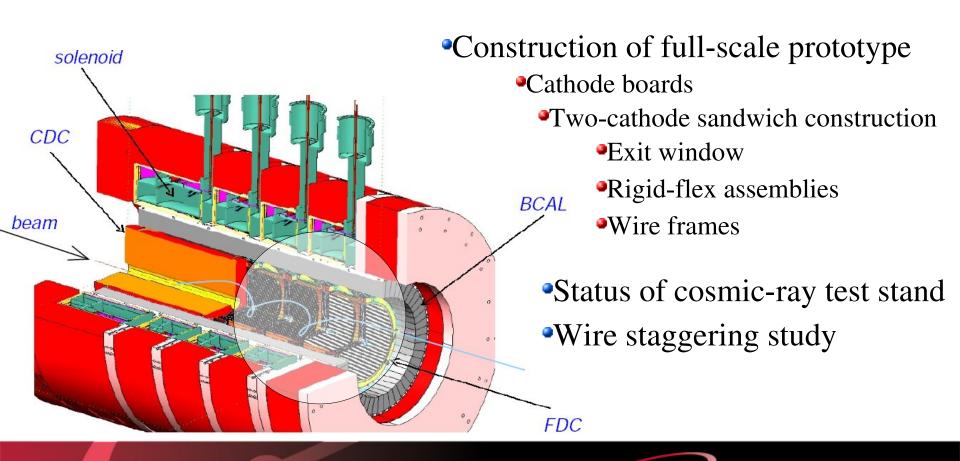

#### FDC Status

Simon Taylor / JLAB

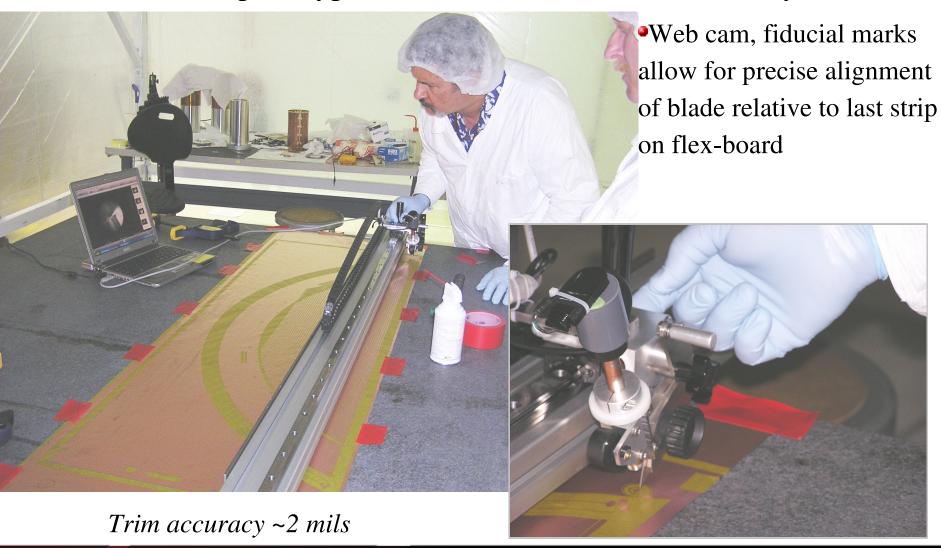

# **Cathode Trimming**

•All the full-scale prototype cathode boards were successfully trimmed

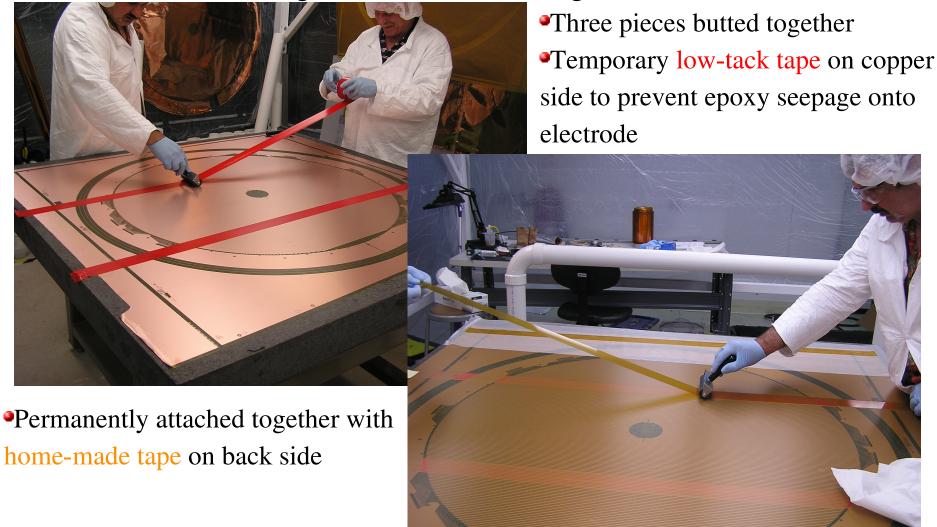

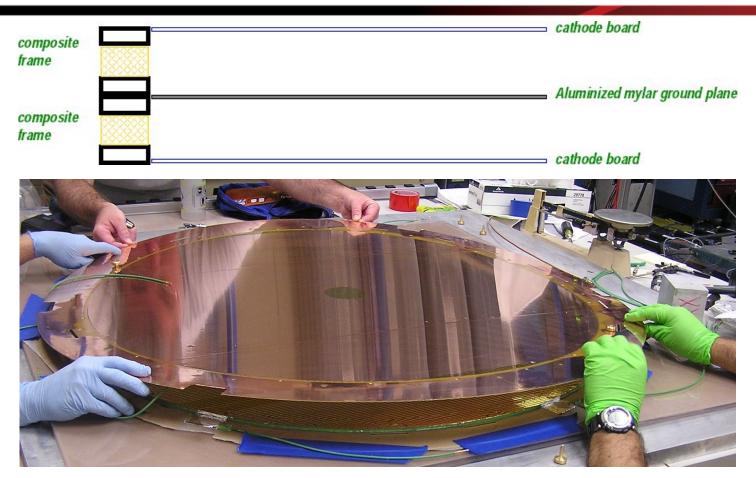

### Three-piece cathode assembly

•Procedure for attaching 3 cathode boards together has been finalized

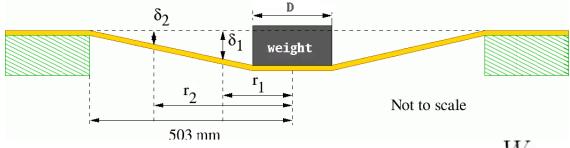

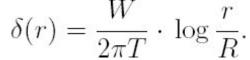

# **Tensioning the Cathodes**

Procedure for tensioning the cathodes has been established

- Use laser sensor to measure deflection

- •Set tension to ~550 N/m

All available cathode boards have been tensioned and epoxied to composite frames

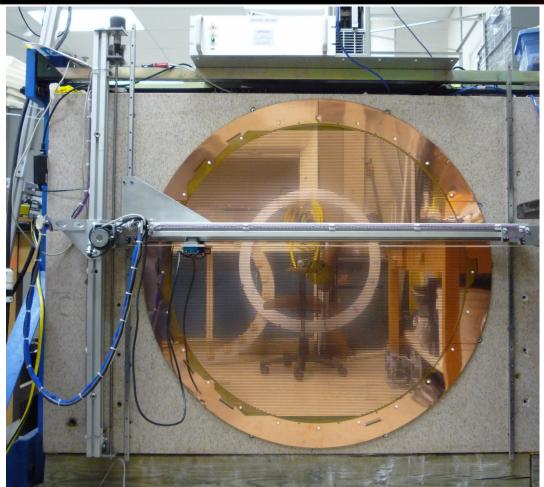

### **Flatness Scans**

Systematic problem on LHS of flatness measurement is not real  $\rightarrow$  under investigation...

Automated scanning in two dimensions using laser scattering

→ check for local variations in flatness (want no wrinkles!)

#### Goal: local flatness < 200 µm

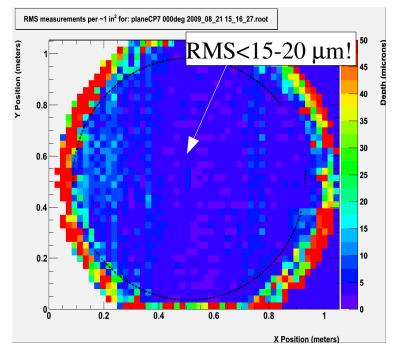

### **Ground Planes**

•Designed to isolate one cathode plane from the next immediately adjacent one

### **Cathode Sandwich Construction**

Two cathode sandwiches have been constructed!

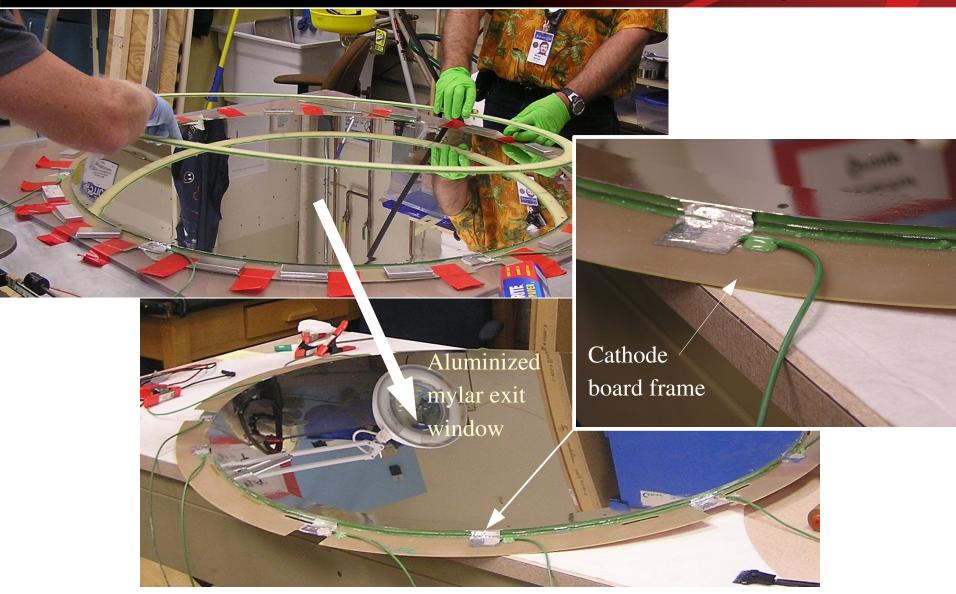

## Exit window+cathode assembly

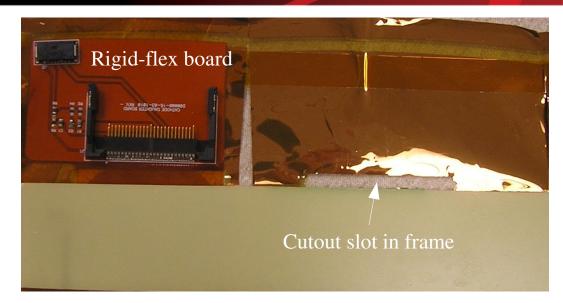

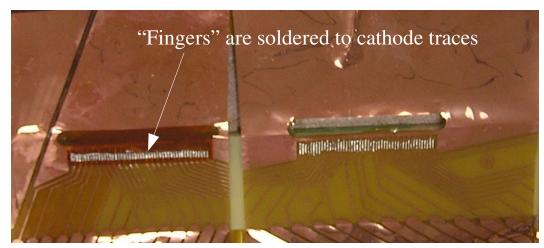

## Rigid-flex board attachment

- •Designed to place connector for the amplifier daughter board on other side of cathode frame relative to the strips

- •For cathode strip readout

- •Space constraints dictate design and placement

- •We are learning how to do the soldering to the traces on the cathode boards

#### Wire Board Issues

- •Initial HV tests → buses drew too much current for wire boards to be usable

- •Further cleaning and HV tests by summer student Rich Rines → current draw reduced

- •Low enough currents only achieved after keeping wire frames in dry environment for ~2 weeks

- •Numerous wire solder joints per board needed repair

- •Solder flux not cleaned off immediately after soldering at IUCF  $\rightarrow$  we needed to do our own cleaning weeks after the fact...

#### Wire Board Issues

•Numerous wire solder joints per board needed repair

•Solder flux not cleaned off immediately

often coldowing at HICF  $\rightarrow$  we needed to do

Current problems on wire frames not eks after the fact... yet solved -- some busses still draw significant currents.

•Initial HV tests → buses ( planes are usable! current for wire boards to b

•Further cleaning and HV student Rich Rines  $\rightarrow$  current draw reduced

•Low enough currents only achieved after keeping wire frames in dry environment for ~2 weeks

## **Phase-3 Wire Winding**

- •We are sub-contracting the winding of the wire frames for the real FDC detector out to IUCF

- •Work to set up Phase 3 contract taking place this Fall

- •Hope to start wire winding toward end of 2010

- •Several remaining issues need to be addressed:

- Plane flatness issues

- Design of wire positioning combs

- New strongback design

- •UCF winding facility modifications (e.g. control electronics)

- Board cleaning specifications

### **Test Stand Status**

Test stand now operational in EEL after move from Test Lab

### **Results for Small-scale Prototype**

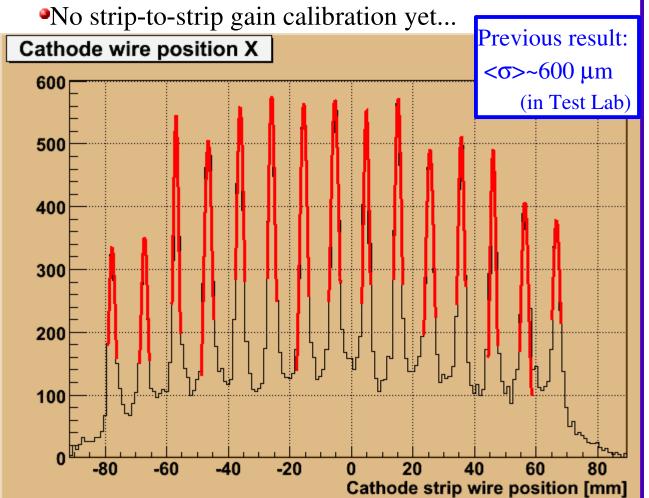

•Cathode centroids used to compute wire position

| wire | pos(mm) | σ(mm) |

|------|---------|-------|

| 0    | -77.7   | 1.2   |

| 1    | -67.2   | 1.2   |

| 2    | -57.0   | 1.0   |

| 3    | -46.5   | 1.4   |

| 4    | -36.1   | 1.3   |

| 5    | -25.9   | 1.2   |

| 6    | -15.5   | 1.3   |

| 7    | -5.4    | 1.5   |

| 8    | 4.8     | 1.1   |

| 9    | 15.1    | 1.3   |

| 10   | 25.5    | 1.4   |

| 11   | 35.6    | 1.2   |

| 12   | 46.0    | 1.0   |

| 13   | 56.3    | 1.3   |

| 14   | 66.7    | 1.4   |

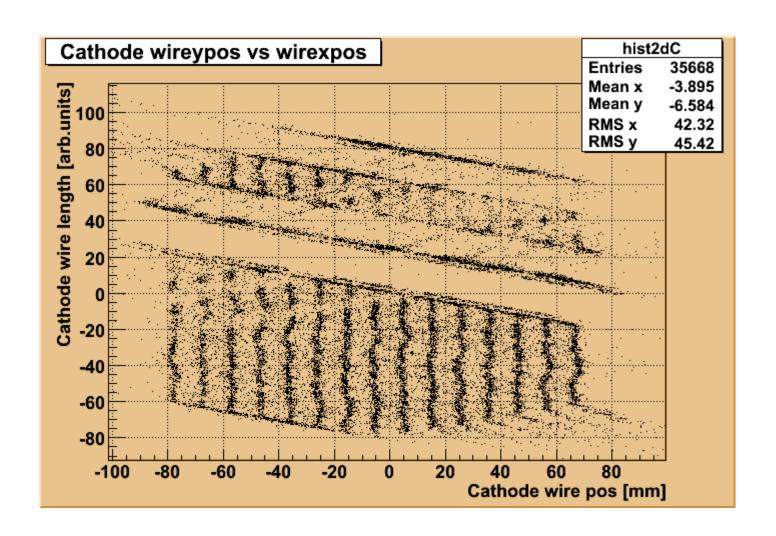

### **Reconstructed Wire Pattern**

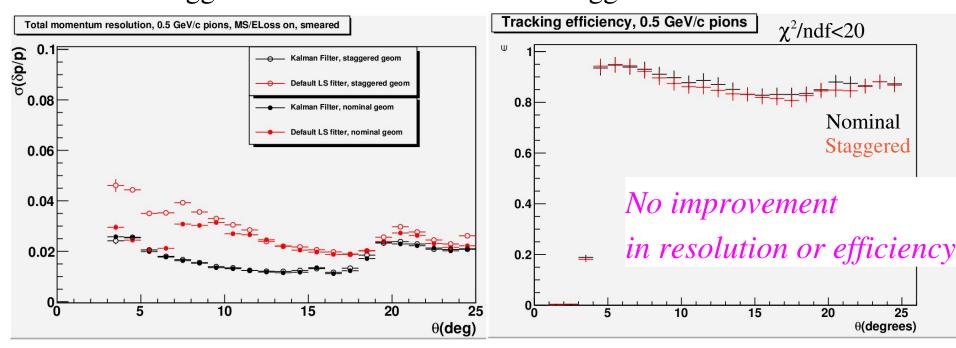

# Staggered wire position option

- •Many drift chamber designs have a UU' configuration where wires in 2 adjacent planes are parallel but offset by a half-cell → aid in resolving "Left-right ambiguity"

- •Nominal FDC design: adjacent planes are rotated with respect to each other, but no wire stagger → should we do the wire stagger also?

Wire staggering is not recommended for FDC design

## **Summary and Outlook**

- •Much progress over the last few months in construction of full-scale prototype

- •This represents the much-appreciated work of many people:

- •Fernando Barbosa, Stephen Burnett, Dan Carman, Eugene Chudakov, Bill Crahen, Roger Flood, Brian Kross, Rich Rines, Kim Shinault, Armen Stepanyan, Mark Stevens, Simon Taylor, Micah Veilleux, Herun Yang, Beni Zihlmann...

- •Cosmic-ray test stand almost fully operational, will be ready to use when prototype is completed

- •Production winding of wire frames will likely take place toward the end of 2010