### **GlueX Collaboration Meeting**

### **12GeV Trigger Electronics**

### 28 January 2010

#### R. Chris Cuevas

- 1. FY10 Project Goals

- Follow up from Sept '09 Meeting

- Notes from other workshops

- 2. Hardware Design Status

- Module Updates

- Final VXS pair mapping

- 3. Schedule

- FY11 and beyond

# FY10 Goals

### • <u>**B**</u>aseline <u>**I**</u>mprovement <u>**A**</u>ctivities (BIA) have been established for FY10

#### FADC250 Rev-

Revision includes 12bit ADC and consolidation of FPGA which will reduce part count significantly. Use latest Xilinx technology and include new requirements.

#### ≻ F1-TDC Rev-2

Revision includes 48 channel 'mode' for FDC, add VXS signaling, upgrade FPGA, add event RAM, and pulse output feature.

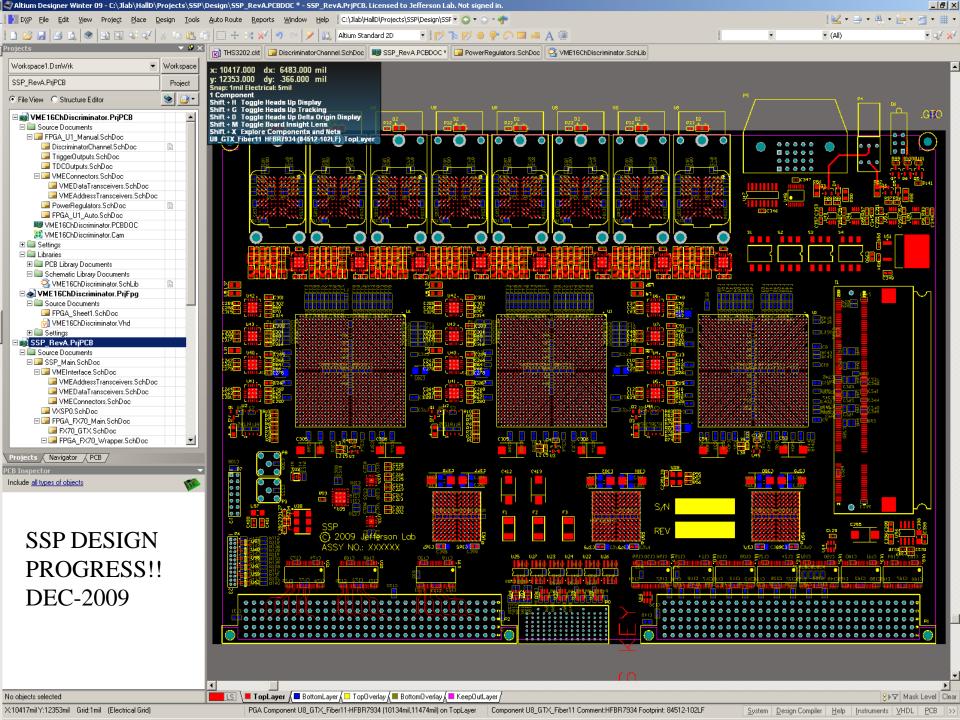

### ➤ SSP (Prototype)

Complete schematic, board layout, assembly, and firmware for at least two units.

### ➢ GTP (Prototype)

Complete schematic, board layout, assembly and firmware for a single unit.

Complete VXS crate specification and procurement for ALL VXS crates needed for 12GeV applications. Allows for quantity price reduction and 'phased' delivery during installation period.

### New Trigger Requirements From Trigger Workshop

#### • Summary

- 1. Use the two trigger signals, Trig1 and Trig2 to change the mode of the flash board readout. Presently the readout mode is selected when the User programs the module before starting a 'run'. Presently the mode does not change during a 'run'. Using the two Trigger bits, the trigger supervisor can issue a specific readout mode for a given trigger event type. (e.g. Change mode to initiate a scaler readout event)

- 2. Dedicate a VXS differential pair from the TI to CTP and from the TI to the SD. Keep the I^2C link, but a differential pair will be needed to transfer data from the two switch cards at a higher rate than the I^2C allows. (The dedicated pair is not required to be a gigabit serial link.)

- Add input/output signaling capabilities to the CTP and TI front panels. The number and type of signaling levels were not defined, but I/O signals will be required and allow for a number of useful features

- 4. Global Trigger -- Implement multiple trigger partitioning "sessions". Ed and David A. outlined a simple idea for up to 4 concurrent trigger sessions using CODA3.

- Global Trigger The Trigger Supervisor will need to manage external signals for calibration systems. Presently the TS is specified to connect directly to the Global Trigger Processor(s) and the additional inputs/outputs to pulsers or other hardware will need to be managed.

- There have been a number of presentations and reviews that have been completed since the June '09 12GeV Trigger Workshop @ CNU:

- CLAS Collaboration June '09

- ✤ S & T Review July '09

- EIC Collaboration Nov '09 @Jlab

- EIC Collaboration Jan '10 @Stoney Brook

- I am delighted that other groups have a keen interest in the plans and performance of the new 12GeV trigger modules and system design.

- Trigger functions on the front end FADC250 have also been developed for use on 6GeV experiments. These developments and work efforts will be very useful for performance benchmarks, and firmware can be reused for future FPGA upgrade.

H. Dong

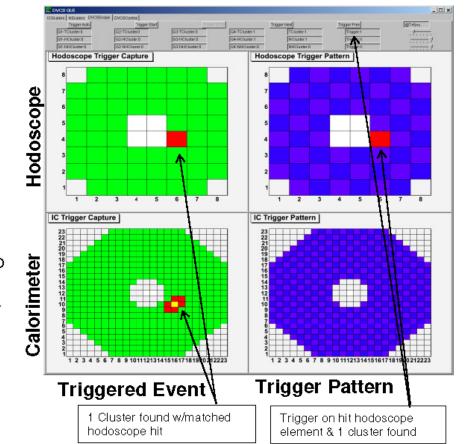

#### PREx -- HALL A Moller Polarimeter Application

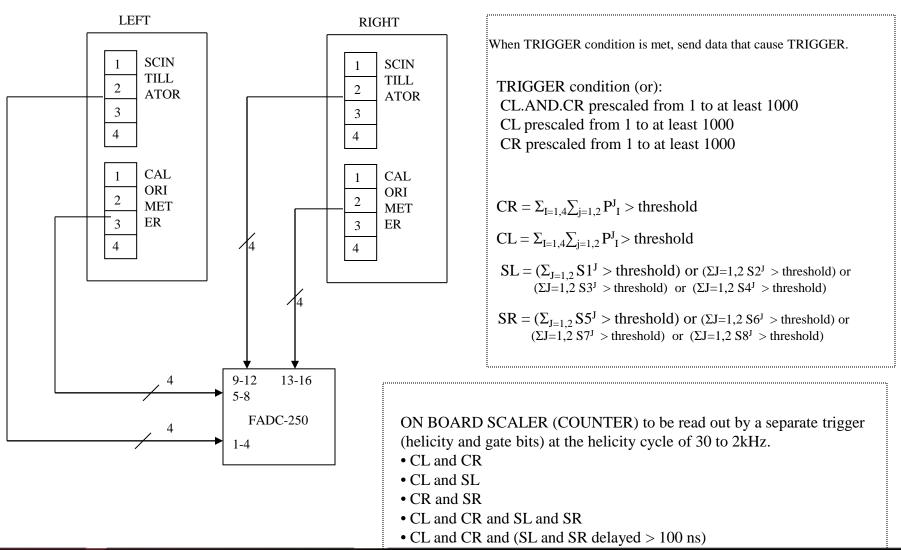

# 5.3 IC Cluster Finding Trigger

B. Raydo

#### 424 Tower PbWO<sub>4</sub> Calorimeter & 56 Channel Hodoscope

- FPGA based trigger finds all clusters with calorimeter by considering all possible views with a 3x3 "sliding" window

- Cluster decisions can optionally be geometrically matched with hodoscope

- Decision time ~85ns, 66MHz pipeline

- Trigger module has a parallel diagnostic trigger that allows arbitrary triggers to be setup for algorithm/channel/timing verification (does not interfere with data taking)

Trigger application example Implemented with CAEN1495

## **Hardware Design Status**

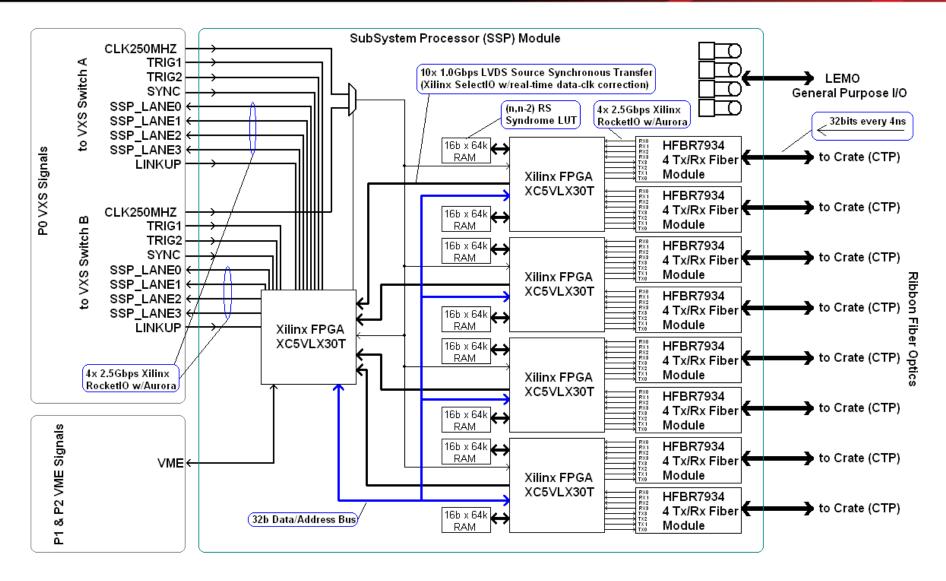

SubSystem Processor (Prototype by end of FY10) Ahead of schedule Schematic complete Component placement complete Preparing for routing Firmware development on track

Global Trigger Processor (Prototype by end of FY10)

Specification has been created and reviewed

Schematic not started

Schedule dependent on additional EE (Position open)

Crate Trigger Processor (No work plan for FY10) Two prototypes successfully tested! (FY09)

Final revision in FY11 work plan

Signal Distribution switch (No work plan for FY10) Two prototypes successfully tested! (FY09)

Final revision in FY11 work plan

## **Hardware Design Status**

Trigger Interface/Trigger Distribution (Latest revision by end of FY10)

Work activity schedule created (William Gu; Ed Jastrzembski)

Initial version of TI/TD successfully tested FY09

Latest revision specification document has been updated

Latest revision will be a single board design with TI/TD functionality

Schematic capture progressing nicely

Initial component placement has started

Board routing strategies to be developed

Firmware development on track

• *Trigger Supervisor* (FY11 work plan) Specification has been created and reviewed Detailed work activity schedule will be created

## **Specification Status**

• **VXS powered card enclosures** (Procurement by end of FY10) Crate specification has been created and ordering strategy discussed with procurement department. Multi-year procurement with delivery quantities per year to be determined.

Trigger System Fiber Optics (FY11 work plan)

Draft system diagram has been specified

Final component specifications will need to be completed and ordered in FY11

🛞 🔁

## **Global Trigger Processor: (GTP)**

## Trigger Interface (TI) Trigger Distribution (TD)

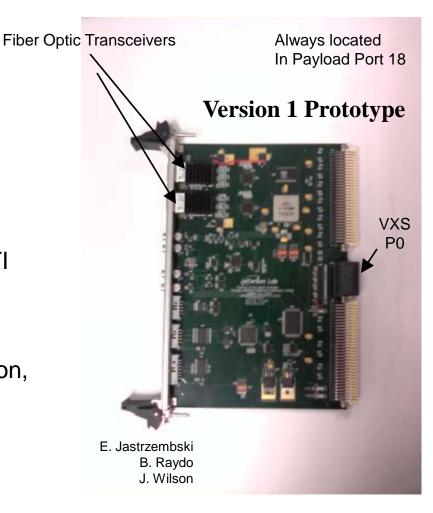

VXS payload board format

Provides communication from VME to SD & CTP modules via I^2C serial links.

• Version 1 Prototype shown and was successfully tested with two VXS crates.

• William Gu has updated the specification and one circuit board design will be used for both TI or TD configuration.

• Direct fiber optic link to Trigger Supervisor crate. Receives precision clock, synchronization, and trigger signals, plus trigger link status.

• Interfaces directly to crate SD module via the VXS backplane.

• Manages local trigger even buffers and interrupts to crate <u>Read-Out Controller (ROC)</u>

STATUS

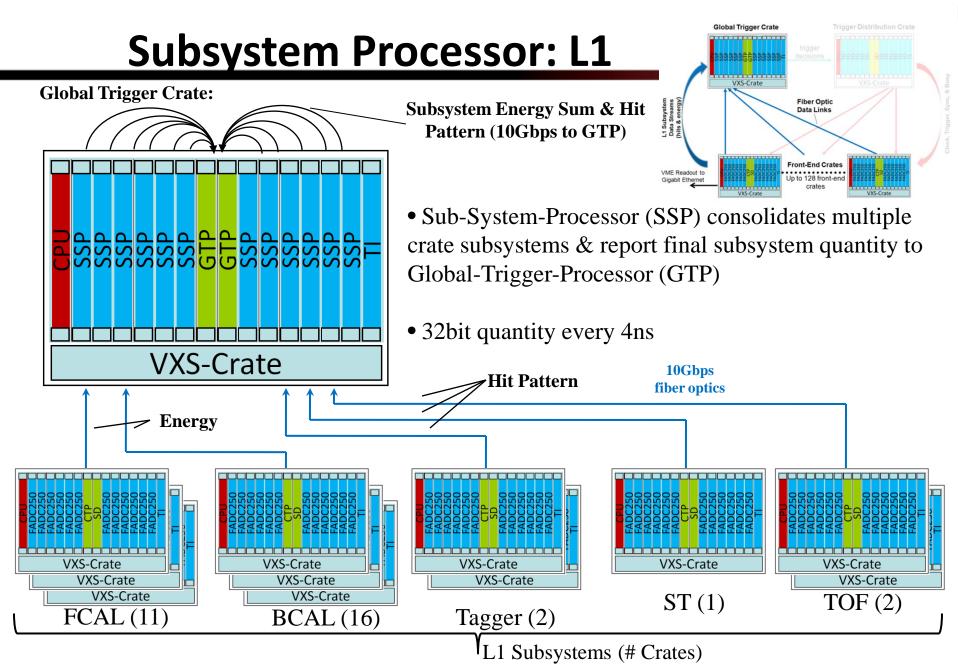

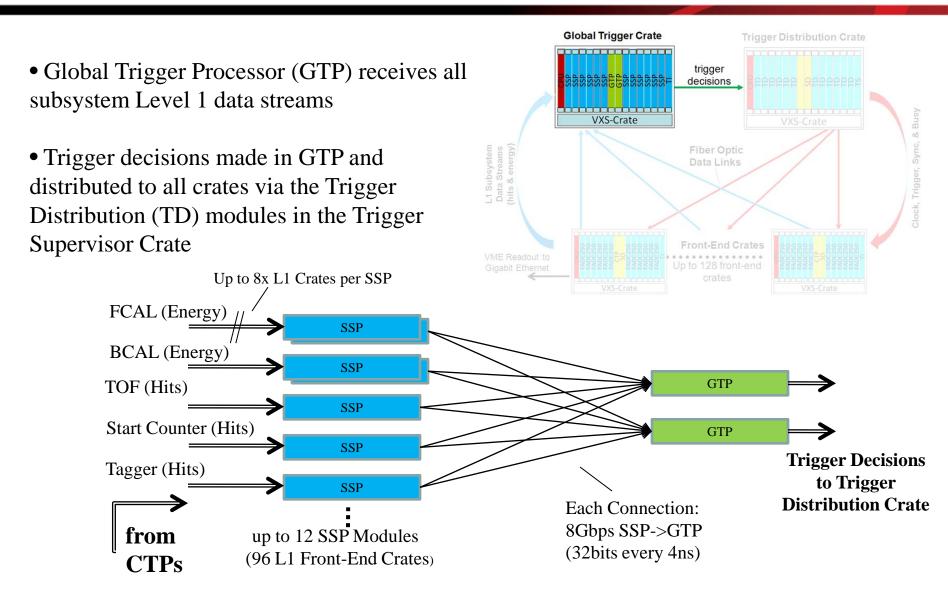

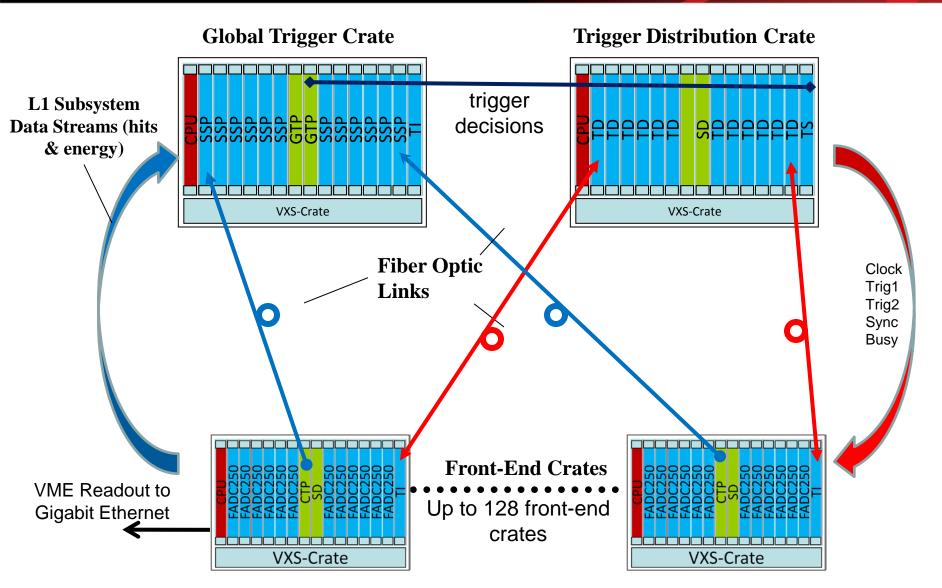

## Level 1 & Trigger Distribution

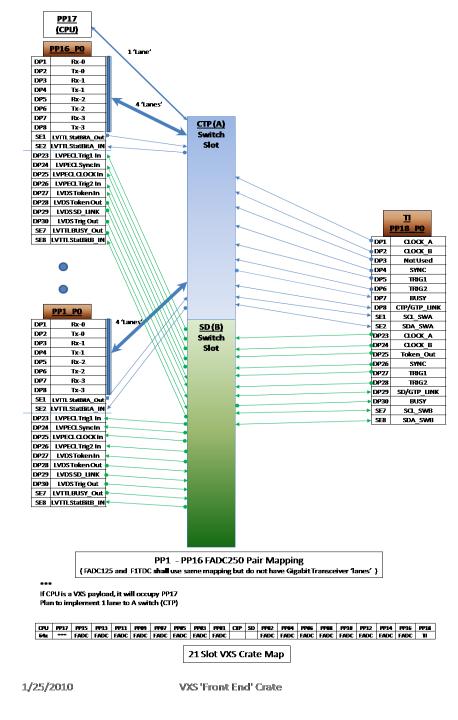

## Front-End Crate VXS Pair Map

- Final configuration

- Other groups will use these definitions for their custom payload modules

- Careful consideration for use of SD and TI boards in the Global Trigger Crate

F1-TDC and FADC125 crates will not require CTP

**STATUS**

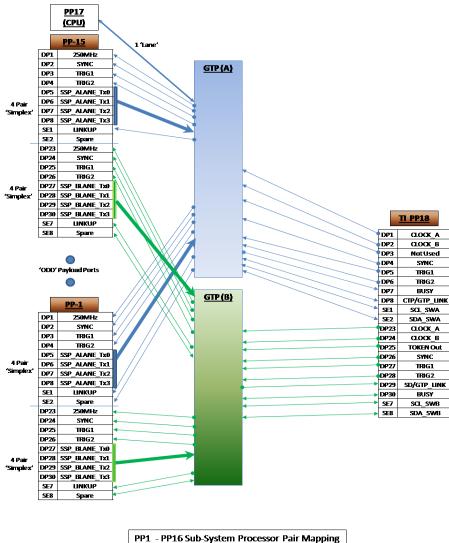

Global Trigger Crate VXS Pair Map

• SubSystem Processors are Payload board format and will communicate with two GTP

### •Note TI mapping is identical to Front-End Crate

(Eight SSP shown in crate map table below) (64 Front-End Crates )

If CPU is a VXS payload, it will occupy PP17 Plan to implement 1 lane to both GTPA and GTPB

OPU

PP17

PP13

PP13

PP14

PP46

PP46

PP46

PP46

PP12

PP14

PP16

PP18

64x

\*\*\*

SSP

<

21 Slot VXS Crate Map

1/25/2010

....

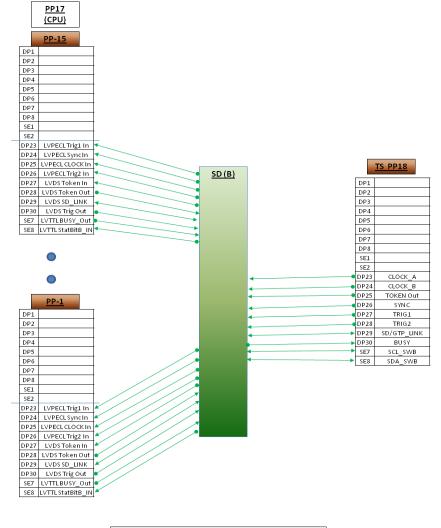

PP1 - PP16 Trigger Distribution Pair Mapping (8 Trigger Distribution (TD) shown in crate map table below) (64 Front-End Crates)

\*\*\*

If CPU is a VXS payload, it will occupy PP17

| CDU   | PP17 | PP15 | 0012 | PP11 | PP09 | PP07 | PP05 | PP03                          | 0001           | C14/A        | CIM/D       | 0003 | 0004 | PP06 | PP08 | 0010 | PP12 | 0014 | PP16 | 0019 |

|-------|------|------|------|------|------|------|------|-------------------------------|----------------|--------------|-------------|------|------|------|------|------|------|------|------|------|

| CPU   | PP17 | PP15 | PP15 | PP11 | PP09 | PP07 | PPUS | PPUS                          | PPUI           | SVVA         | 3 V V D     | PPUZ | PP04 | PPU6 | PPU8 | PPIU | PP1Z | PP14 | PP10 | PP10 |

| 64x   | ***  |      |      |      |      | TD   | TD   | TD                            | TD             |              | SD          | TD   | TD   | TD   | TD   |      |      |      |      | тs   |

| /26/2 | 2010 | )    |      |      |      |      | S    | 21 Slo<br>V><br>upei<br>istri | (S "T<br>rvisc | rigg<br>pr/T | ger<br>rigg | er   | >    |      |      |      |      |      |      |      |

**Trigger Supervisor Crate** (Trigger Distribution) VXS Pair Map

Trigger Distribution (TD) are Payload board format and will communicate TS via a Signal Distribution (SD) switch module

### •Note TD mapping is identical to Front-End Crate

## Schedules, work plans for FY11 - FY13

- FY10 design projects are at full resource pace!

- ► FADC250

- ≻ F1TDC-V2

- ≻ SSP

- ≻ TI-TD

- > 16 Channel Discriminator/Scaler (Hall B requirement)

- VXS Crate Specification

- ➢ GTP (Need EE full time,)

- > Other non-trigger board projects are on-going also, but not the focus of this talk.

- Request from Larry to review work plans and budgets for FY11- FY13

- Broadly, the Hall D project plan lists substantial amounts for labor for installation and testing activities in the Hall for Trigger/DAQ and Electronics for FY11 – FY13

- Several of the board projects listed above will be available before FY11 begins

- FY11 will be an intensive year of significant 'system' level testing to assure that these boards are ready for final production quantity orders.

## Schedules, work plans for FY11, FY12

#### Selected WBS activities extracted from Hall D project plan: Labor only

#### 1.5.4.2 F1TDC-V2

|         | •               |                                                |                                         |         |          |        |        |                                    |

|---------|-----------------|------------------------------------------------|-----------------------------------------|---------|----------|--------|--------|------------------------------------|

|         | Start           | Finish                                         | Activity                                |         |          | Start  | Finish | Activity                           |

|         | \$56,569 Jul-11 | Dec-11                                         | Install Crates                          |         |          |        | Mar-09 | All F1 Chips ORDERED!              |

|         | \$64,526 Dec-11 | May-12                                         | Install Cabling                         |         | \$68,304 | Dec-10 | Feb-11 | Test TDC timing with Discriminator |

|         | \$47,414 Apr-12 | Oct-12                                         | Install Trigger Electronics             |         | \$84,919 | Feb-11 | Apr-11 | Implement TDC firmware Test        |

|         | \$94,828 Dec-11 | May-12                                         | Install Readout Electronics             |         | \$84,919 | Apr-11 | Jun-11 | Dry run of test procedures         |

|         | \$27,675 May-12 | Aug-12                                         | Check out CH Daq Equip                  |         | \$3,316  | Jan-12 | Apr-12 | Receive TDCs                       |

|         | \$27,675 May-12 | Aug-09                                         | Check out cabling                       |         | \$6,632  | Apr-12 | Jul-12 | Burn in testing                    |

|         | \$29,176 Oct-12 | 76 Oct-12 Jan-13 Check out Trigger Electronics |                                         |         | \$16,580 | Jul-12 | Nov-12 | Acceptance testing single board    |

|         | \$29,176 May-12 | Sep-12                                         | Check out Readout Electronics           |         | \$8,290  | Nov-12 | Apr-13 | Crate testing                      |

|         |                 |                                                |                                         | 1.5.4.3 | TRIGGER  |        |        |                                    |

| 1.5.4.1 | FADC250         | Jan-12                                         | ORDER 625 modules!!!!!!                 |         |          | Start  | Finish | Activity                           |

|         | Start           | Finish                                         | Activity                                |         | \$15,914 | Jul-11 | Aug-11 | Receive Crate Trigger Processor    |

|         | \$84,919 Dec-10 | Feb-11                                         | Test feature extraction firmware        |         | \$15,914 | Aug-11 | Oct-11 | Burn In test                       |

|         | \$84,919 Feb-09 | Mar-11                                         | Implement Summing and test              |         | \$26,524 | Oct-11 | Dec-11 | Acceptance Testing                 |

|         | \$6,632 Oct-12  | Nov-12                                         | Receive production modules              |         | \$79,548 | Dec-11 | Apr-12 | Multi-crate Testing                |

|         | \$13,264 Oct-12 | Dec-12                                         | Test and burn in                        |         | \$15,914 | Jul-12 | Aug-12 | Receive balance of CTPs            |

|         | \$16,580 Dec-12 | Feb-13                                         | Acceptance Testing                      |         | \$15,914 | Aug-12 | Oct-12 | Burn In test                       |

|         | \$8,290 Feb-13  | Mar-13                                         | Test in crates                          |         | \$21,219 | Oct-12 | Dec-12 | Single board acceptance of GTP     |

|         | \$11,385 Mar-13 | Jun-13                                         | Assemble and test with Trigger          |         | \$79,548 | Dec-12 | Apr-13 | Crate acceptance testing           |

| 1.5.6.2 | INSTALLATION    |                                                |                                         |         | \$53,040 | Oct-11 | Jan-12 | GTP and TS testing                 |

|         | Start           | Finish                                         | Activity                                |         | \$53,048 | Jul-12 | Dec-12 | Full Assembly of TS crate sys      |

|         | \$16,975 Aug-12 | Sep-12                                         | Complete Installation of Readout System |         | \$15,914 | Dec-12 | Jan-13 | Burn in test of TS sys             |

|         | \$16,580 Jun-13 | Jul-13                                         | Install Trigger Electronics ALL         |         | \$15,914 | May-13 | Jun-13 | Board acceptance test of TS        |

|         | \$12,598 Sep-13 | Oct-13                                         | Test of Trigger Electronics             |         |          |        |        |                                    |

| 1       |                 |                                                |                                         |         |          |        |        |                                    |

\$12,598 Oct-13 Nov-13 Hall Test of Readout System

1.5.3.1 DAQ

## Summary

- FY10 board design projects are on track

- **GREAT WORK** on keeping these projects on schedule

- Work activities exceed EE and E-Designer resources, but we push forward,

- GTP design activities must be started soon independent of new EE hire status

- Delighted to see that other groups are contributing trigger application ideas and providing important benchmark results.

- FINAL VXS pair mapping has been established so other groups (Hall A, Hall B) are able to start their custom VXS payload modules.

- Weekly 12GeV Trigger meeting has produced good discussions and ideas for implementation of system level test programs that will be essential for commissioning the DAQ/Trigger/Readout system in the Hall.

- Looking forward, the FY11 FY13 schedule appears to be reasonable, (labor \$\$ included), but detailed work activities will need to be created to assure success.

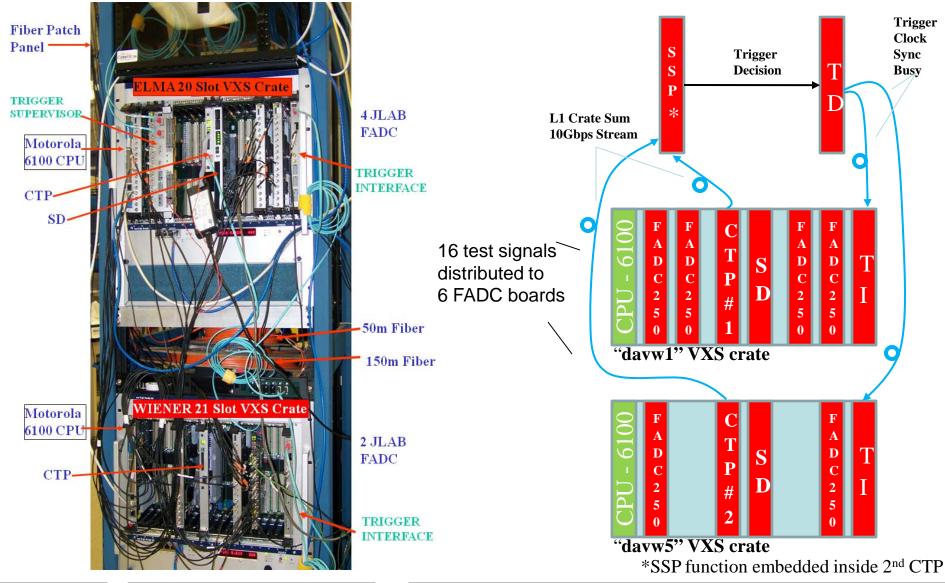

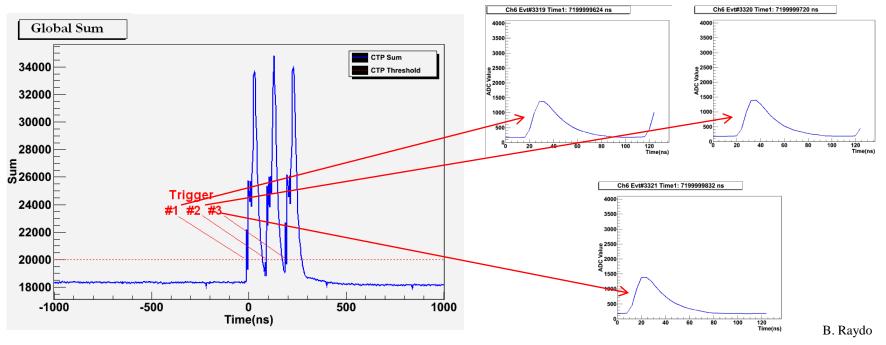

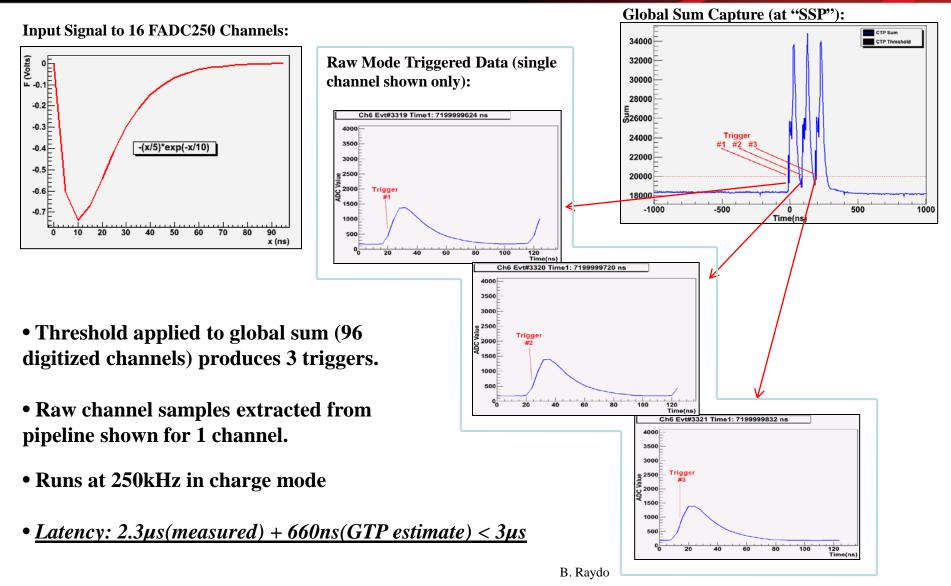

## Level 1 Hardware Test Results

## **2 Fully Prototyped Front-End Crates**

## **Synchronized Multi-Crate Readout**

- CTP #2 is also acting as an SSP (by summing the local crate + CTP#1 sum over fiber

- A programmable threshold is set in CTP, which creates a trigger when the global sum (6 FADC boards => 96 channels) is over threshold.

- Example test with a burst of 3 pulses into 16 channels across 2 crates/6 FADC modules

A 2µs global sum window is recorded around the trigger to see how the trigger was formed:

#### Example Raw Event Data for 1 FADC Channel:

# **2 Crate Energy Sum Testing**

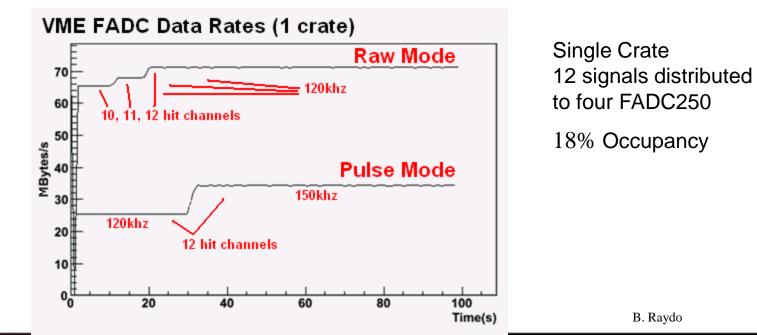

### **Synchronized Multi-Crate Readout Rates**

- FADC event synchronization has been stable for several billion events @ ~150kHz trigger rate.

- Have run up to 140kHz trigger rate in raw window mode, up to 170kHz in Pulse/Time mode.

- Ed Jastrzembski has completed the 2eSST VME Interface on FADC allowing ~200MB/s readout

## **SSP Block Diagram**

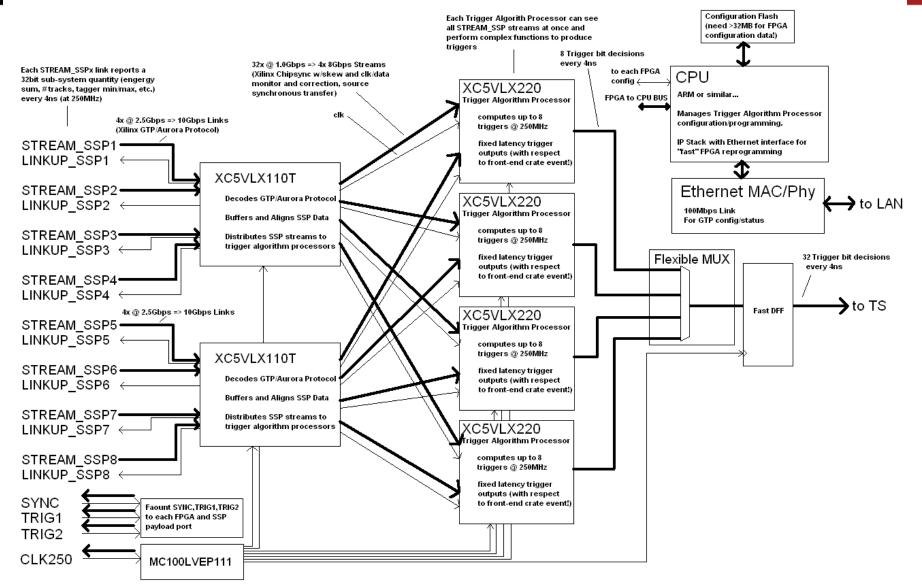

## **GTP Block Diagram**

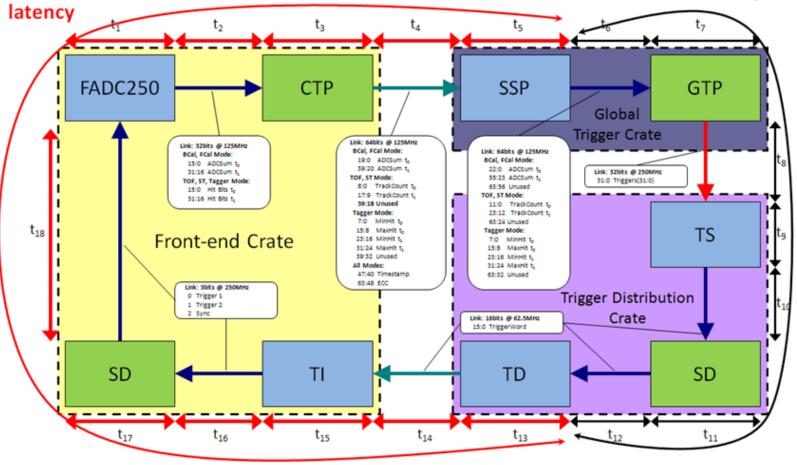

# **GlueX Level 1 Timing**

#### 2.3µs measured

660ns estimated latency remaining

2.3µs (measured) + 660ns (estimated) < 3µs!

Fiber Optic Link Copper Ribbon Cable VXS Backplane