#### **GlueX Collaboration Meeting**

### **12GeV Trigger Electronics**

#### 2-4 February 2011

#### R. Chris Cuevas

- 1. Hardware Design Status Updates

- The regular list of acronyms SD; TI-D; SSP; CTP; GTP; TS

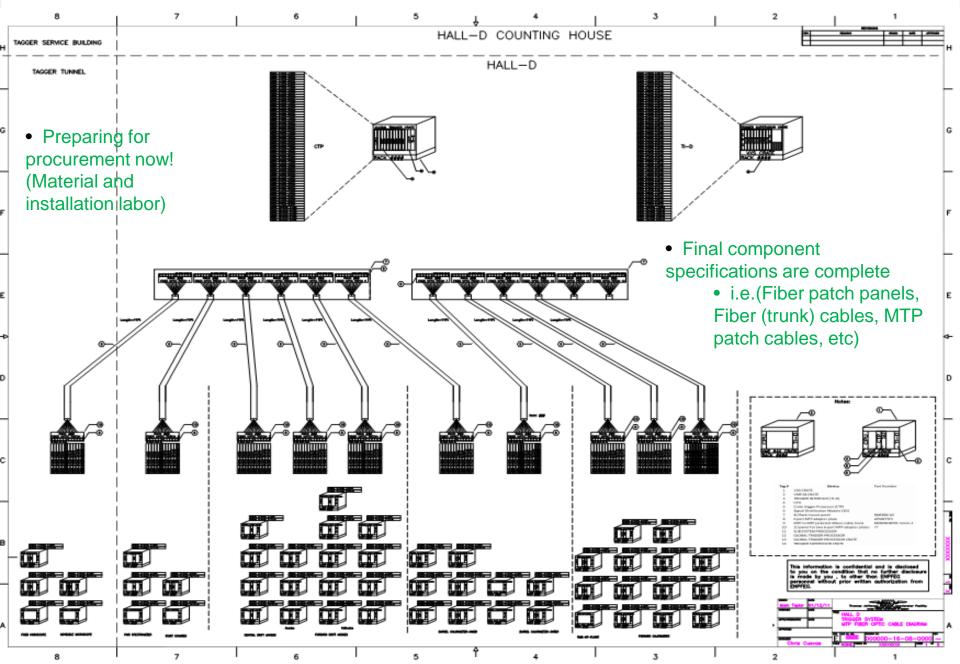

- Trigger System Fiber Optics

- Preparation for full crate testing

- 2. 1<sup>st</sup> Article VXS Crate Testing

- 3. Summary

- <u>Flash</u> <u>ADC</u> 250Msps (FADC250)

- $\checkmark$  This is where the trigger 'data' begins

- ✓ \*\* Version 2 design complete See Fernando's update \*\*

- ✓ Many tests have been completed!

- ✓ Significant layout revision with consolidation of firmware and FPGA

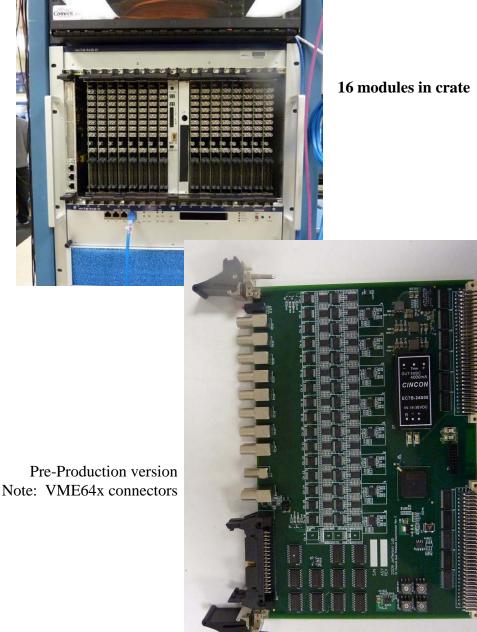

- <u>C</u>rate <u>Trigger</u> Processor ( CTP )

- ✓ \*\* 2 units tested in 2009 \*\* 2 more sent for assembly Sept-2010

- ✓ 2 new CTPs assembled and received. New modules have different FPGA and support higher Gigabit speed (5Gbps)

- ✓ Initial CTP used for verification of new WIENER VXS backplane

- $\checkmark$  New boards will be thoroughly tested and used in full crate test plan

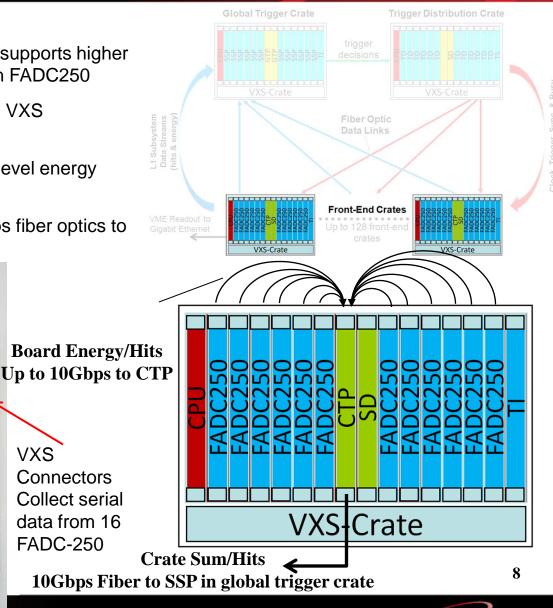

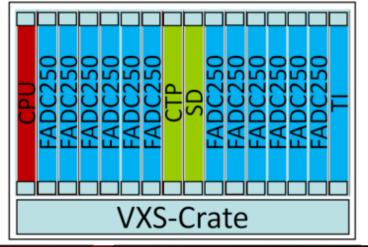

- ✓ Collects trigger data (SUM) from 16 FADC250 modules within one crate

- ✓ Transports trigger data over fiber to Global Trigger crate

- 10Gbps capability (8Gbps successfully tested)

- <u>Signal</u> <u>D</u>istribution (SD)

- ✓ 2 prototypes tested in 2009 \*\* Rev-1 ready to manufacturer Oct-2010 \*\*

- Precision low jitter fan-out of ADC clock, trigger and synch signals over VXS backplane to FADC250 modules

- ✓ Minor revisions to include clock jitter attenuation PLL

- ✓ 2 Rev-1 boards have been assembled and received

- ✓ A few power supply issues have been resolved, and updates to firmware have been completed to support jitter attenuation PLLs

- ✓ I^2C communication with latest TI-D has been tested

- $\checkmark$  We have components for at least six more units

- ✓ Two boards will be used for full crate testing before ordering preproduction quantities. (June 2011)

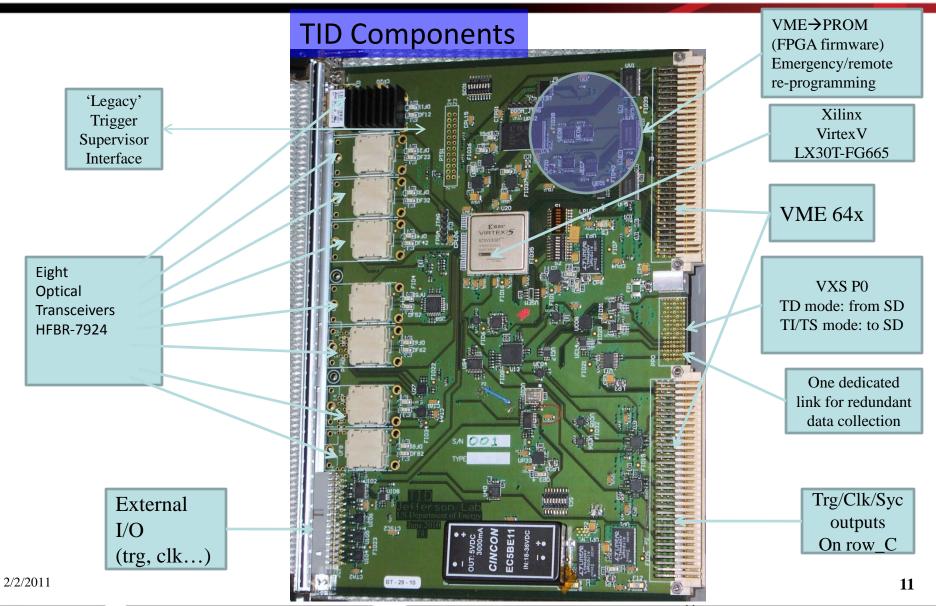

- <u>Trigger</u> Interface <u>Trigger</u> Distribution (TI TD)

- ✓ FY10 Goals achieved.

- ✓ FY11 test goals are ahead of schedule and firmware has been completed.

- Design changes have been recorded and peripheral modules for TI-D have been completed. (i.e. Fan-out board for CAEN V1290 TDC)

- ✓ CODA library has been updated for latest TI-D revision.

- ✓ After full crate testing, pre-production quantities will be ordered.

- ✓ Direct link to Trigger Supervisor crate

- $\checkmark$  Distributes precision clock, triggers, and sync to crate SD

- ✓ Manages crate triggers and ReadOut Controller events

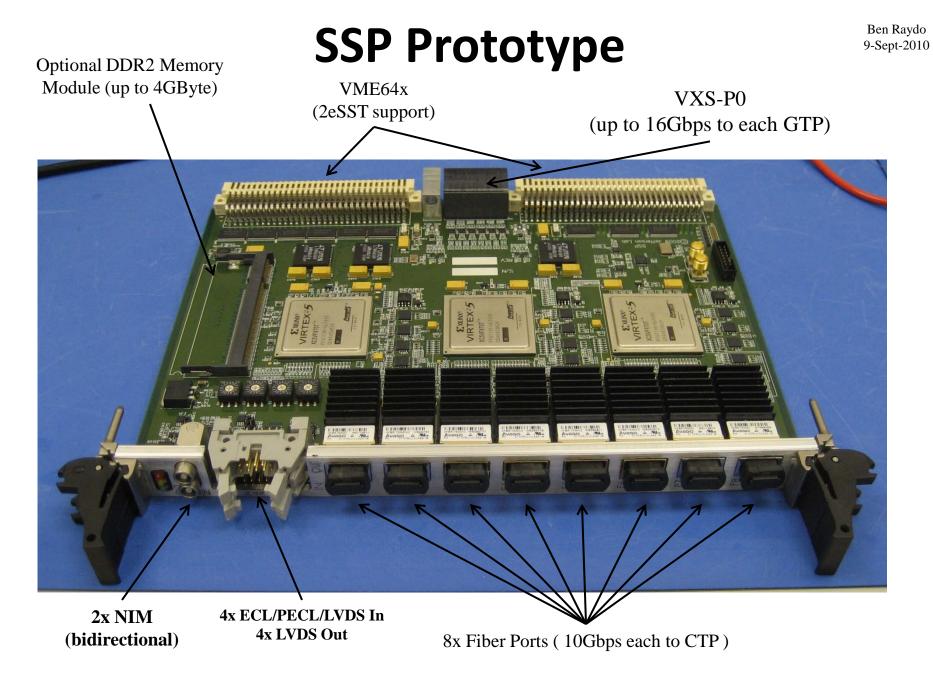

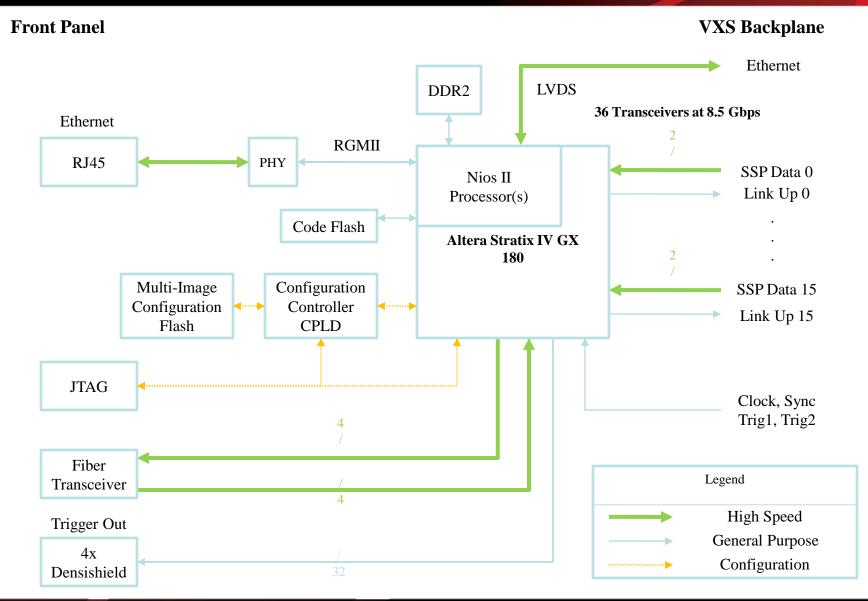

- <u>Sub</u>System <u>Processor</u> (SSP)

- ✓ Prototype received and is undergoing detailed functional testing!!

- ✓ FY10 goals achieved and FY11 test activities will continue

- ✓ Will use SSP during full crate testing in the spring

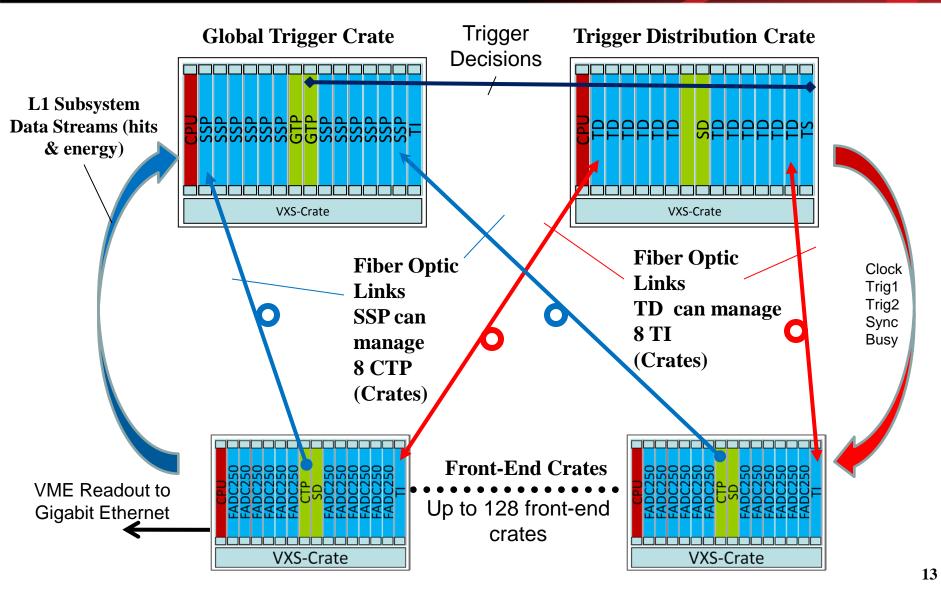

- ✓ Collects trigger data from up to 8 front end crates. (2048 channels!)

- ✓ Trigger data received on front panel with fiber transceivers

- ✓ 10Gbps input capability ( 4 lanes @3.125Gbps\*(8/10b) )

- ✓ 10Gpbs output stream to GTP

- <u>G</u>lobal <u>Trigger</u> Processor ( GTP ) (FY10-11)

- ✓ Schematic work is back on schedule (Scott Kaneta )

- ✓ FY11 goal is to build initial prototype and test with SSP and TI-D

- $\checkmark$  Revisions to initial specification has been updated and finalized

- ✓ Interface requirements to SSP and TS have been finalized

- Large scale FPGA has been selected and Xilinx Aurora protocol has been tested with Altera FPGA

- <u>Trigger Supervisor (TS)</u> (FY11-12)

- ✓ New board format VXS Payload module

- $\checkmark$  Distributes precision clock, triggers, and sync to crate TI-TD

- ✓ Manages crate triggers and ReadOut Controller events

- ✓ Direct cable link to Global Trigger Processor (32 trigger bits)

- ✓ Specification has been updated to match GTP output

- Schematic and board layout activities can begin after full DAQ crate testing is complete and pre-production orders for TI-D and other boards have been completed.

#### Ben Raydo

#### **Discriminator Status** (Not truly trigger system hardware, but very nice new development)

- 16 Pre-Production modules have been assembled and received

- Significantly cheaper than V895: -cost < \$2,000

- Provides several features not found on V895: -32bit scalers on all channels at both thresholds

- -Calibrated pulse widths: from 8 to 40ns

-Trimmed input offset (<2mV error)</li>

-Second 34pin output connector is fully programmable.

- -Able to perform logic based on all channels at both thresholds

- Final revision has VME64x J1-J2 connector

- Full test stand developed by Pedro Toledo(USM Chile) will be re-used

- Hall Groups will test with detectors

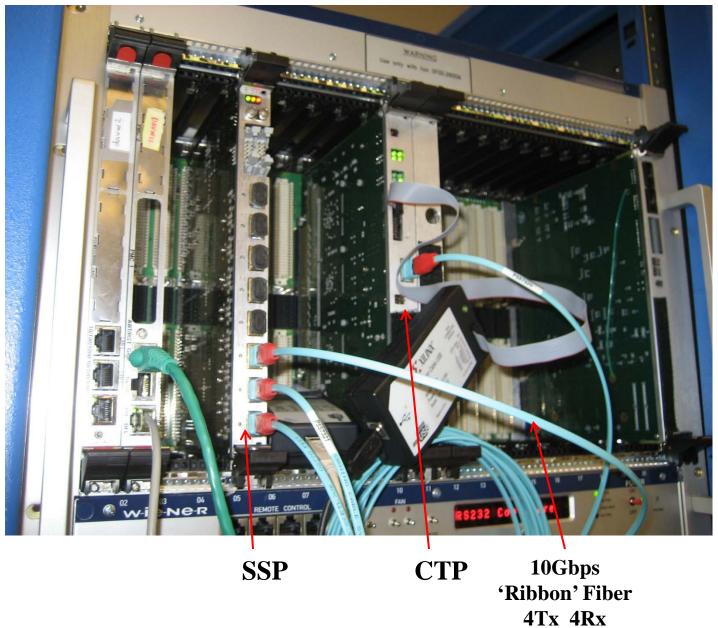

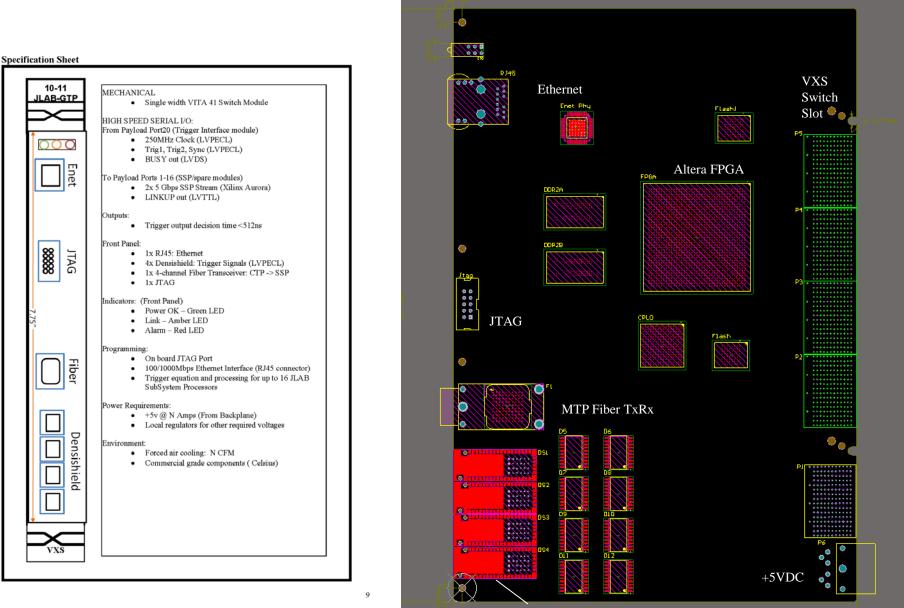

## **Crate Trigger Processor**

- 4 Fully assembled units are in the lab!!

- 2 newest units include VirtexV FX70T that supports higher serial speeds. (5Gbps) Matches FX70T on FADC250

- Initial CTP unit used to verify new WIENER VXS backplane map

- Crate Trigger Processor computes a crate-level energy sum (or hit pattern)

- Computed crate-level value sent via 10Gbps fiber optics to Global Trigger Crate (32bits every 4ns)

Jefferson Lab

CTP

**Prototype:**

Fiber Optics Transceiver

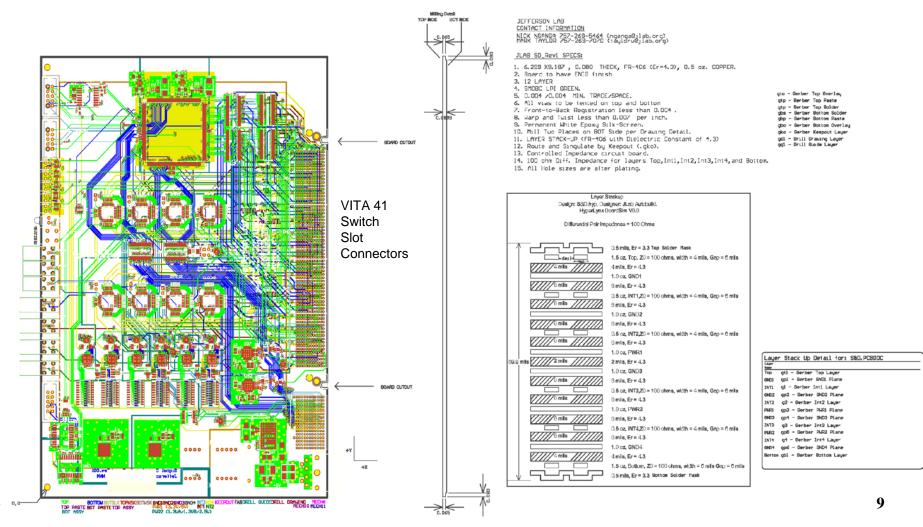

### Crate Level – Signal Distribution (SD) -Rev 1

N. Nganga 10-Oct-2010

Two boards fully assembled and almost completely tested

### Crate Level – Signal Distribution (SD) -Rev 1

- New power regulation scheme tested

- New (final) front panel complete

- Token In/Out tested

- Latest I^2C firmware has been tested with TI-D. Supports the control of the on board PLLs from the FPGA via SPI. Users can select Jitter Attenuation mode (PLL) or non-PLL mode.

- All common signals from TI (i.e. Busy, Sync, Trig1, Trig2 have been tested.

- Final results from PLL jitter attenuation tests will be completed before 15-Feb-2011

## **Trigger Interface - Distribution**

Jefferson Lab

W. Gu DAQ Group

### What is tested:

- $\checkmark$  The power distribution for the board is tested and working.

- ✓ All the discrete components (drivers, buffers, receivers etc) are tested, and working

- $\checkmark$  The on-board clock distribution network is working.

- ✓ The on-board trigger distribution network is working.

- ✓ Serialized trigger data re-sampling (ADN2805).

- ✓ FPGA firmware:

- VME to I2C engine;

- VME data readout;

- VME remote firmware loading;

- Customized the firmware for TI, TD, mini-TS mode

- Initial Jitter analysis results for 250MHz clock are low <u>~2ps</u>

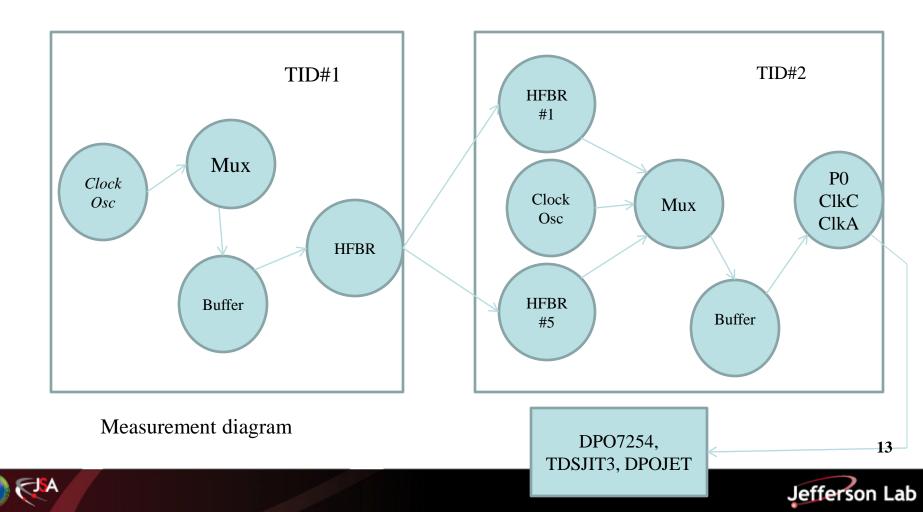

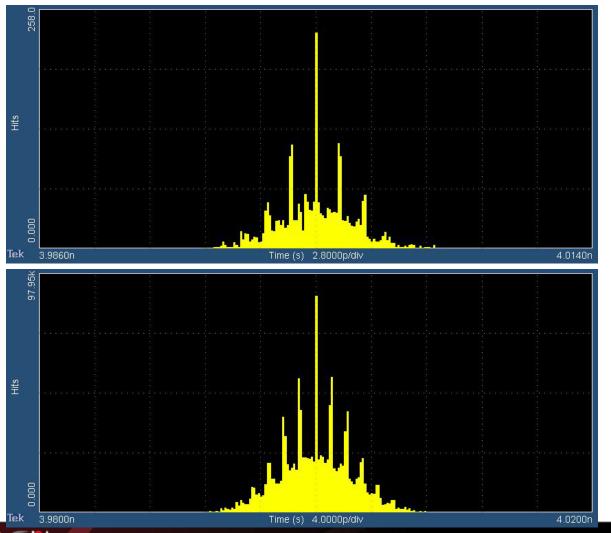

## **TI-TD Testing**

W. Gu DAQ Group

The scope used: Tek7254, probe: TDS3500 differential probe Scope setting: 40GS/sec → 25 Ps/Pt, 2.5 GHz limited Measuring software: TDSJIT3 ADVANCED, 400K samples (auto set) or DPOJET ESSENTIAL, 50M samples. Measured on TID#2, TID#1 may be used as clock source

## **TI-TD Testing**

W. Gu DAQ Group

Assuming that the oscillator has negligible jitters, the TID to P0 distribution has a jitter of less than 2ps, and the two HFBR\_7924/34 distribution has a jitter of less than 2ps too (sqrt(2.65\*2.65-1.88\*1.88)=1.87ps).

TID#2 on-board oscillator as clock source, the ClkC jitter measured: 1.88ps

TID#2, HFBR#5 as clock source, the ClkC jitter measured: 2.65ps

**SSP Working with CTP**

Ben Raydo 9-Sept-2010

# SSP 2.5Gbps Fiber Eye (1 of 32 shown)

Gigabit transceivers & optics are performing much better than device specifications – further testing will reveal accurate bit-error rate estimates.

Ben Raydo

## **SSP Summary**

- BGA assembly issues have been resolved.

- SSP will be used for two DAQ crate testing in spring.

- Link quality tests remain between fibers and FPGAs, as well as FPGA and FPGA, but is looking very good so far.

- DDR2 Memory testing needs to be completed

- Testing with GTP will have to wait for GTP prototype. (June '11)

- SSP Project ahead of schedule!

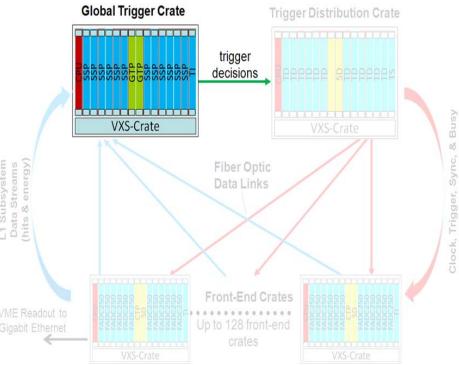

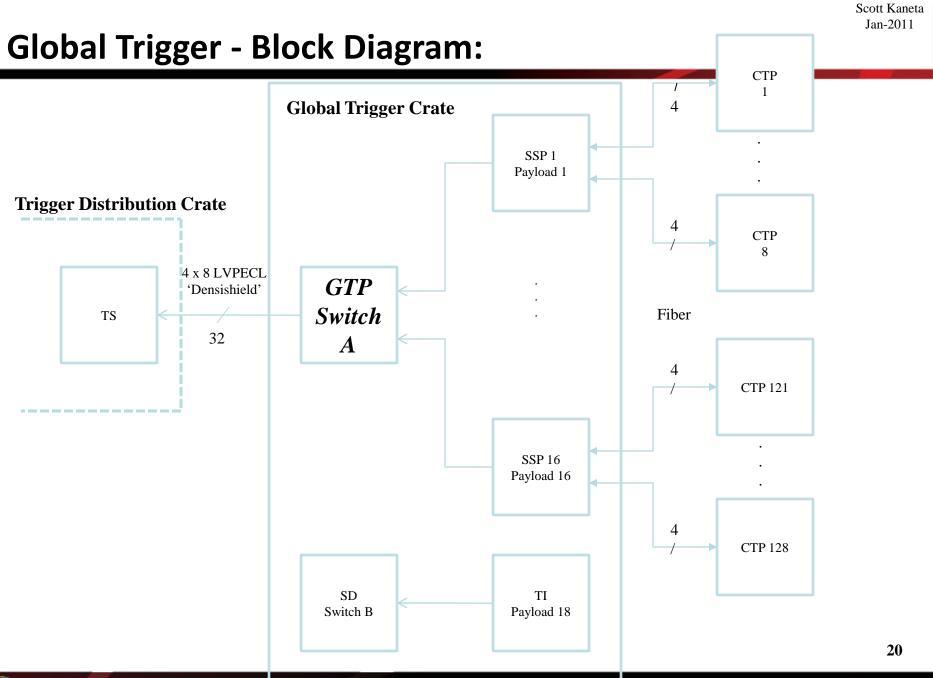

### **Global Trigger Processor: (GTP)**

- Global Trigger Processor (GTP) receives al subsystem Level 1 data streams from SSP

- Trigger decisions made in GTP and distributed to all crates via the Trigger Distribution (TD) modules in the Trigger Supervisor Crate

- Schematics and component selection activities are progressing well

- Preliminary component placement and layout strategies have been completed

- Xilinx's 'Aurora' Gigabit protocol has been ported to Altera device successfully

Trigger Decisions to Trigger Distribution Crate {Trigger Supervisor}

19

lefferson Lab

🍘 💎

Scott Kaneta Jan-2011

21

Jefferson Lab

### **Global Trigger Processor: (GTP)**

Scott Kaneta Jan-2011

### **Global Trigger Processor: (GTP)**

LVPECL 4 x 8 pair to TS (P2)

## **Other Trigger System Essentials**

#### • VXS and VME64x powered card enclosures

- ✓ Crate specification complete

- ✓ Multi-year contract awarded to W-IE-NE-R, Plein & Baus, Ltd.

- ✓ First article crates (VXS) received 24-Jan-2011

- ✓ Acceptance tests nearly complete

- ✓ (6) -> VME64x & (8) -> VXS crates will be delivered before May-2011

<u>Will need storage location!!</u>

Hartman VXS 21 Slot Backplane CTP @2.5Gbps to each payload port Correctly mapped

| concert mapped                                                |    |       |         |      |           |      |       |      |         |         |           |         |     |                                         |

|---------------------------------------------------------------|----|-------|---------|------|-----------|------|-------|------|---------|---------|-----------|---------|-----|-----------------------------------------|

| 🎯 Waveform - DEV:2 MyDevice2 (XC5VLX110T) UNIT:0 MyILAO (ILA) |    |       |         |      |           |      |       |      |         |         |           |         |     |                                         |

| Bus/Signal                                                    | х  | 0     | 325 365 | 405  | 445       | 485  | 525   | 565  | 605     | 645     | 685       | 725     | 765 | 805                                     |

| <pre></pre>                                                   | EA | EA    |         |      | (1,1,1,1) |      |       |      | 1.1.1.1 | 1.1.1.1 | (1,1,1,1) | 0.000   |     | 1.1.1.1                                 |

| <pre>- /encoder_in&lt;0&gt;</pre>                             | 0  | 0     |         |      |           |      |       |      |         |         |           |         |     |                                         |

| <pre>- /encoder_in<l></l></pre>                               | 1  | 1     |         |      |           |      |       |      |         |         |           |         |     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| <pre>- /encoder_in&lt;2&gt;</pre>                             | 0  | 0     | ההההההה | າທາກ | າດກາດ     |      |       | ոոու | ուսու   | ուսու   | INNIN     | MM      | MM  | າທາກ                                    |

| <pre>- /encoder_in&lt;3&gt;</pre>                             | 1  | 1     | mm      | ллл  | ா         | M    | ЛЛ    | տ    | ЛЛ      | บบา     | யா        | UU      | ா   | UП                                      |

| <pre>- /encoder_in&lt;4&gt;</pre>                             | 0  | 0     |         |      |           | ГП   |       |      |         |         |           |         |     |                                         |

| <pre>- /encoder_in&lt;5&gt;</pre>                             | 1  | 1     |         |      |           |      |       |      |         |         |           |         |     |                                         |

| <pre>- /encoder_in&lt;6&gt;</pre>                             | 1  | 1     |         |      |           |      |       |      |         |         |           |         |     | 1                                       |

| /encoder_in<7>                                                | 1  | 1     |         |      |           |      |       |      |         |         |           |         |     | 1                                       |

| - /encoder_k                                                  | 0  | 0     |         |      |           |      |       |      |         |         |           |         |     |                                         |

| <pre> /decoder_out&lt;5&gt; </pre>                            | C7 | C7    |         |      | (1,1,1,1) |      |       |      | 1.1.1.1 | 1.1.1.1 | (1,1,1,1) | e e e e |     | 1.1.1.1                                 |

| <pre>- /decoder_out&lt;5&gt;</pre>                            | 1  | 1     |         |      |           |      |       |      |         |         |           |         |     |                                         |

| <pre>- /decoder_out&lt;5&gt;</pre>                            | 1  | 1     |         |      |           |      |       |      |         |         |           |         |     | nnnnn                                   |

| <pre>- /decoder_out&lt;5&gt;</pre>                            | 1  | 1     |         | מממת | տու       | התתת | າດດາດ |      | տոր     | ທາກນ    | uuuu      | սոող    | WWW | NNN                                     |

| <pre>- /decoder_out&lt;5&gt;</pre>                            | 0  | 0     | mm      | ЛЛ   | ய         | ЛЛ   | ЛЛ    | ากก  | JUU     | nn      | տո        | ΠΠ      | M   | UU                                      |

| <pre>- /decoder_out&lt;5&gt;</pre>                            | 0  | 0     |         |      |           | П    |       |      |         |         | பா        |         |     |                                         |

| <pre>- /decoder_out&lt;5&gt;</pre>                            | 0  | 0     |         |      |           |      |       |      |         |         |           |         |     |                                         |

| <pre>- /decoder_out&lt;5&gt;</pre>                            | 1  | 1     |         |      |           |      |       |      |         |         |           |         |     |                                         |

| /decoder_out<5>                                               | 1  | 1     |         |      |           |      |       |      |         |         |           |         |     |                                         |

| <pre>- /decoder_k&lt;5&gt;</pre>                              | 0  | 0     |         |      |           |      |       |      |         |         |           |         |     |                                         |

| 1                                                             |    | · · · |         |      |           |      |       |      |         |         |           |         |     |                                         |

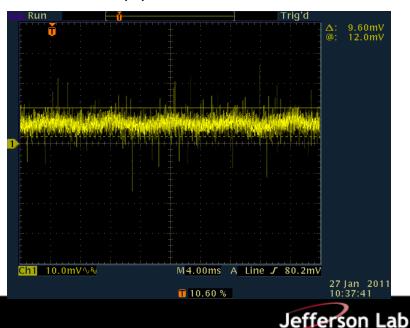

+5VDC; Ripple Measurement <10mVp-p; 50A load

#### Other Trigger System Essentials Trigger System Fiber Optics FY11 Work Plan

System diagrams have been updated for Hall D installation

24

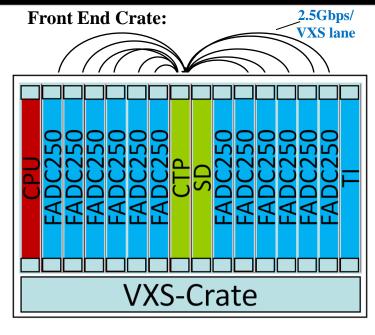

## **Two DAQ Crate Testing: FY11**

- Several modules have been revised and will need to be thoroughly tested. (FADC250, SD, TI-D)

- The initial SSP will be used to sum the trigger data from 2 CTP

• Multiple crate 'system level' testing is imperative before approving large quantity orders.

- Will verify Gigabit serial lanes from each slot

- 1<sup>st</sup> Time for 16 boards!!!

- Will measure trigger latency

- Will measure trigger rates/VME data rate

- Will measure BitErrorRates

- Will test using "Playback" mode

- (No input cables necessary)

- Perfect opportunity to fully test latest revision of CODA board 'libraries'

- Plan to use latest CPU as proposed by DAQ group

### Summary

- FY10 board design project goals have been achieved

- FY11 plan includes aggressive test plans for all modules

- GTP prototype and completion of *FINAL* revisions for trigger modules in FY11

- High level of detailed design work is exemplary and board tests meet specification

- Work activity schedule shows estimate to completion plan is reasonable

- o Production quantities for all halls have been considered

- 2 full DAQ crates with all trigger module units will be tested in spring

- Time to think about 4th annual 12GeV Trigger Workshop

- $\circ~$  Will have plenty of results from full crate testing

- Plenty of other work remains for pre-commissioning 'tools' and test plans

- Weekly 12GeV Trigger meeting continues to produce good discussions and ideas for implementation of system level test programs and details of hardware designs.

26

## All sorts of good stuff

## **GlueX Level 1 Timing**

#### 2.3µs measured latency remaining latency t4 ts. t7 t<sub>2</sub> t<sub>3</sub> \_ \_ \_ \_ - -FADC250 SSP CTP GTP Global **Trigger Crate** Link: 64bits @ 125MHz Link: 32bits @ 125MHz BCal, FCal Mode: Link: 64bits @ 125MHz BCal, FCal Mode: BCal, FCal Mode: 19:0 ADCSum to 15:0 ADCSum to 39:20 ADCSum t 22:0 ADCSum to 31:16 ADCSum t<sub>1</sub> Link: 32bits @ 250MHz TOF, ST Mode: 55:23 ADCSum t 31:0 Triggers(31:0) TOF, ST, Tagger Mode: 8:0 TrackCount te 63:56 Unused 15:0 Hit Bits to TOF, ST Mode: 17:9 TrackCount te 31:16 Hit Bits to 39:18 Unused 11:0 TrackCount t. Tagger Mode: 23:12 TrackCount t<sub>a</sub> 7:0 MinHit ta 63:24 Unused t<sub>18</sub> 15:8 MaxHit to Tagger Mode: TS et Front-end Crate 23:16 MinHit t, 7:0 MinHit te 31:24 MaxHit te 15:8 MaxHit L 39:32 Unused 23:16 MinHit t<sub>a</sub> All Modes: 31:24 MaxHit t<sub>2</sub> 47:40 Timestamp 63:32 Unused 63:48 ECC Link: 3bits @ 250MHz **Trigger Distribution** 0 Trigger 1 1 Trigger 2 2 Sync Crate Link: 16bits @ 62.5MHz 15:0 TriggerWord SD TD SD TΙ t<sub>14</sub> t<sub>15</sub> t<sub>13</sub> t<sub>17</sub> t<sub>11</sub> t<sub>16</sub>

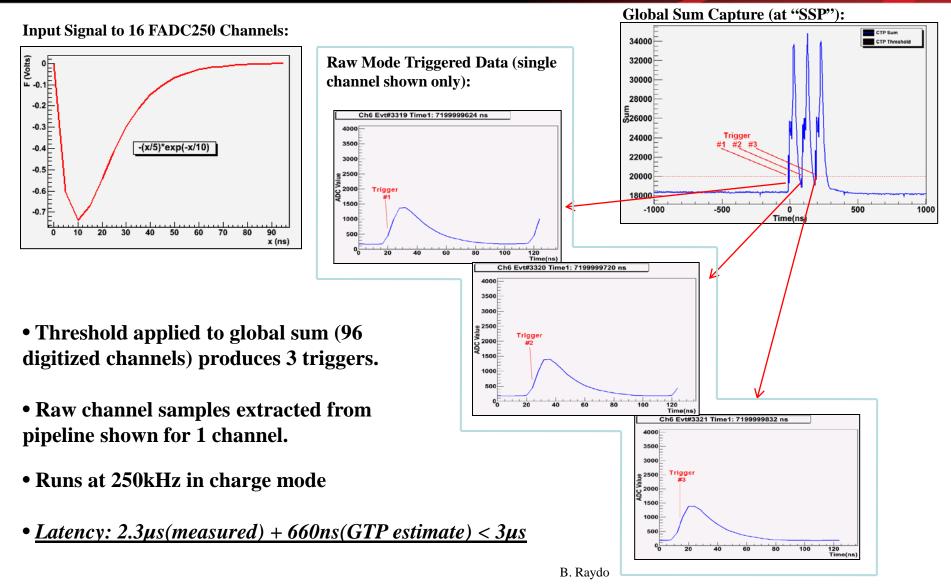

2.3µs (measured) + 660ns (estimated) < 3µs!

Fiber Optic Link Copper Ribbon Cable VXS Backplane

660ns estimated

21

### Schedules, work plans for FY11 - FY13

#### • FY10 design projects are at full resource pace!

- > FADC250  $\rightarrow$  Latest revision at end of FY10. TEST in FY11.

- F1TDC-V2→ Work plan moved to FY11

- SD → Latest revisions virtually complete. Order, assemble, TEST in FY11

- > SSP  $\rightarrow$  Prototype received. Initial testing is proceeding nicely. Further testing in FY11.

- ≻ TI-TD → Prototype(s) received. Initial testing is proceeding nicely.

Firmware development and multi-crate testing in FY11

- > 16 Channel LE Discriminator/Scaler (Hall B requirement)

7 'production' units under test now

- > VXS Crate Specification  $\rightarrow$  Order should be awarded before Oct-10

- > GTP  $\rightarrow$  Scott Kaneta joins the group! GTP slips to FY11

- ➤ TS → Specified, and planned for FY11-FY12

- Baseline Improvement Activities (BIA) review on 17-September

- FY11 will be an intensive year of significant 'system' level testing to assure that these boards are ready for final production quantity orders in early FY12

## Level 1 & Trigger Distribution

## **Synchronized Multi-Crate Readout**

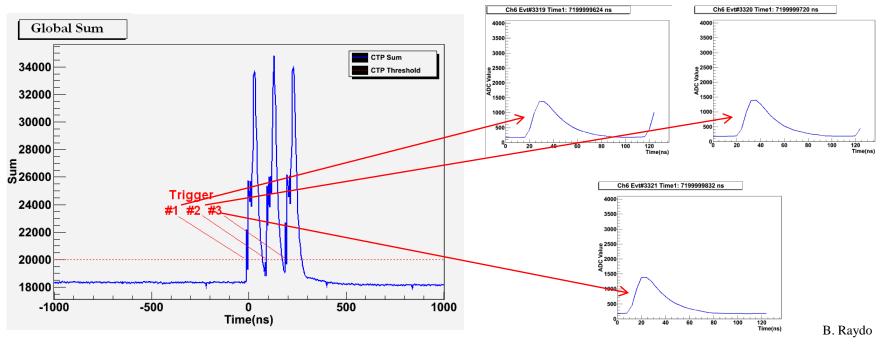

- CTP #2 is also acting as an SSP (by summing the local crate + CTP#1 sum over fiber

- A programmable threshold is set in CTP, which creates a trigger when the global sum (6 FADC boards => 96 channels) is over threshold.

- Example test with a burst of 3 pulses into 16 channels across 2 crates/6 FADC modules

A 2µs global sum window is recorded around the trigger to see how the trigger was formed:

#### Example Raw Event Data for 1 FADC Channel:

## **2 Crate Energy Sum Testing**

### **Synchronized Multi-Crate Readout Rates**

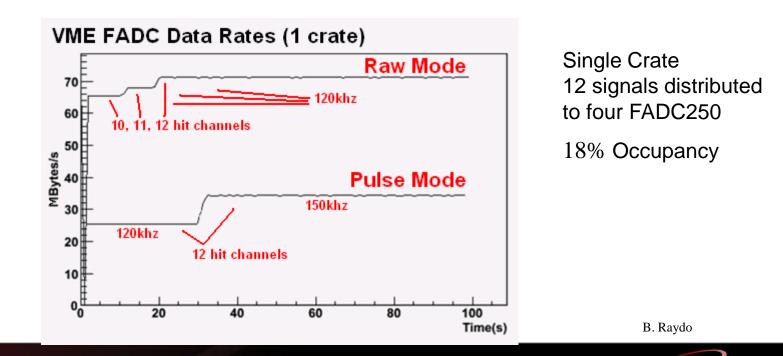

- FADC event synchronization has been stable for several billion events @ ~150kHz trigger rate.

- Have run up to 140kHz trigger rate in raw window mode, up to 170kHz in Pulse/Time mode.

- Ed Jastrzembski has completed the 2eSST VME Interface on FADC allowing ~200MB/s readout

Jefferson Lab