Nuclear Physics Division Fast Electronics Group

# Firmware for VXS Crate Trigger Processor Version 2 (CTPV2) Tagger Module Version 0A01

**April 23, 2014**

**Hai Dong**

# **Table of Contents**

| Title                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Revision                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Introduction                                | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| FX70T (U1, U3) VHDL Code                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| FX100T (U24) VHDL Code                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| I-SQUARE-C Code                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| <b>Total Delay</b>                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| LED                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| SD Test Code                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| <b>Configuring FPGA from I-SQUARE-C Bus</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| <b>Board Serial Number</b>                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Steps to Align Data from FLASH Boards       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Crate ID                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Microscope Trigger Algorithm                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| <b>Hodoscope Trigger Algorithm</b>          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| _                                           | Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Register File                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| <b>Channel to Pay Load Port Mapping</b>     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| MicroScope SSP Bit Mapping                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| HodoScope SSP Bit Mapping                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Front Panel LED                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Front Panel LVDS IN, LVDS OUT               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Appendix                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                             | Introduction FX70T (U1, U3) VHDL Code FX100T (U24) VHDL Code I-SQUARE-C Code Total Delay LED SD Test Code Configuring FPGA from I-SQUARE-C Bus Board Serial Number Steps to Align Data from FLASH Boards Crate ID Microscope Trigger Algorithm Hodoscope Trigger Algorithm Selecting MicroScope or HodoScope Trigger Register File Channel to Pay Load Port Mapping MicroScope SSP Bit Mapping HodoScope SSP Bit Mapping Front Panel LED Front Panel LVDS IN, LVDS OUT |  |

#### 0.0 Revisions:

- 0.1 Version 0A01.

- 0.1.1 History Buffer

- 0.1.1.1 Expand to 32 bits

- 0.1.1.2 Store Hit Bits to SSP

- 0.1.1.3 Is triggered when any of the Concident Hits Bits to SSP that are enable by U24 registers 8 and 9

- 0.2 Front Panel Bit one is either Oring of HodoScope HitBits or Oring of Microscope HitBits.

### 1.0 Introduction

The firmware for the Crate Trigger Module (CTP) is written in VHDL. The CTP module has two XC5VLV50 (U1, U3) that has same VHDL code and one XC5VLV110 (U24) that has its own VHDL code. LV50 VHDL code receives data from five FADC, aligns the data, and sends the data in sync with system clock to the LV110. The LV110 receives data from six FADC and both LV50, aligns the data, processes the data, and sends the result to Fiber located at the front panel.

This firmware has the addition of BCAL processing described in Section 12.0.

### **2.0 FX70T (U1,U3) VHDL Code**

#### 2.1 Receive data from FADC

The VHDL code receives data from five FADC using Xilinx Aurora operating at 2.5Gbits, aligns the data, and sends the data 80 bits synchronized with 250MHz clock. The Aurora protocol provides control and interface signals: Lane\_up, Channel\_up, Rx\_src\_rdy\_n, Tx\_src\_rdy\_n, Tx\_dst\_rdy\_n. The functions for these signals are as follow:

- Lane\_up: indicates FADC MGT and CTP GTP are able to send and receiving data from each other.

- Channel\_up: indicates the data from the lanes if more than one are in alignment.

- Tx\_dst\_rdy\_n: indicates that the transmitter is ready to send data

- Tx src rdy n: tell the transmitter to send user data.

- Rx\_src\_rdy\_n: indicates that the receiver has user data

### 2.2 Aligning Data

In the 12 Gev Trigger System, Sync is distributed in time to all sixteen FADC250V2 and CTP modules in a crate. When Sync goes high, FADC250 stops sending data and CTP reset all its circuitries and buffers. Sync has to be high for at least 500 nS to allow the MGT to completely flush its buffers. When Sync goes low, the FADC250 send value 2 for one 16 bits and value 1 for the other 16 bits on the 2 MGT lanes 0 and 1. Values 2 and 1 are sent 3 times. Which value is sent on lane 0 and 1 is depend on when the Sync arrived at the FADC250. The CTP uses these values to align data from all 16 FADC250 in time and words order. After aligning the data from 5 FADC250, U1 sends data to U24 via 80 LVDS lines. U3 does the same as U1. U24

aligns the data from 6 FADC250, wait for data from U1 and U3, processes, and sends data to SSP through fiber. First Word Fall Through FIFO is used to used to indicate when first values 2 and 1 are received. This process is enable when bit 3 of Config1 is a one.

### **Demultiplexed Data to VLX110 (U24)**

The 32-bits data from each FADC is de-multiplexed into two 16-bits words with bits 31-16 send to U24 first. The 16-bits word is registered (F1\_F3\_D) and sends to U24 along with DatRdy. After Sync goes low, DatRdy goes high along with all values 2 output. DatRdy goes low when Sync goes high. The 250 MHz input clock is routed inside the FPGA to output pins (CLK\_FPGA1\_3). The LV110 uses CLK\_FPGA1\_3 to capture F1\_F3\_D and Datrdy.

### 2.3 Disable FADC

Data from FADC can be disabled by writing to Configuration register via I-square-C interface. When disabled, the code does not wait for data from that FADC250. The bits corresponded to that FADC are zero going.

### 2.4 Processing Delay

### 2.5 Xilinx System Monitor.

Xilinx System Monitor feature that indicates the die temperature and VCCINT and VCCAUX Supply is included. The data is mapped into register file that can be read back through I-Square-C. The host has to convert binary data to temperature and voltage (See Xilinx UG192).

### **3.0 FX100T (U24) VHDL code**

### 3.1 Receive data from FADC

The procedure for receiving data from six FADC is identical to U1 and U3.

### 3.2 Receive data from U1 and U3

When Datrdy is high, 80 bits data is clocked into 512\_80 FIFO. Five-hundred words deep can handle 2uS skewing between the two VLX50. The number of clock from Datrdy going high to data FIFO empty going low is 8 (32 ns).

### 3.3 Aligning Data.

Aligning data from six FADC250 is the same as U1 and U3. When Datrdy from U1 goes high, U24 allows words from U1 to be written into First-Word-Fall-Through FIFO. It does the same with U3. When words values of 2 are at the output of these FIFO, the FIFO are read at the same time. This process is enable when bit 3 of Config1 is a one.

### 3.4 **Summing Data.**

The data is de-multiplexed and add in stages as shown below. The stages are used to make 250 MHz clocking using Xilinx FPGA lowest cost (speed grade 1).

### 3.4.1 First stage

- $1^{st}$ \_A0 = VLX50 #1 bit (15..0), (31..16), (47..32)

- $1^{st}$ \_A1 = VLX50 #1 bit (63..48), (79..64)

- $2^{\text{nd}}$ \_A0 = VLX50 #2 bit (15..0), (31..16), (47..32)

- $2^{\text{nd}}$  A1 = VLX50 #2 bit (63..48), (79..64)

### 2.1.2 Second stage

- $1^{st}_B = 1^{st}_A + 1^{st}_A$

- $2^{\text{nd}} B = 2^{\text{nd}} A0 + 2^{\text{nd}} A1$

- $SUM_A = FADC_0 + FADC_1 + FADC_2$

- $SUM_B = FADC_3 + FADC_4 + FADC_5$

### 2.1.3 Third stage

- $1^{st} 2^{nd} = 1^{st} B + 2^{nd} B$

- SUMA B = SUMA + SUMB

### 2.1.4 Fourth stage

• Final\_SUM =  $1^{st}_2^{nd}$  + SUMA\_B

### 3.5 Multiplexing Final SUM

In the CTP the FIBER data consisted of 4 Aurora Lanes operating at 2.5Gibits. Each lane provides 16bits for a total of 64-bits every 8 NS. Since the 20-bits Final Sum is occurring at 4 NS, two Final Sum is packed (multiplexed) into one transmission. Final Sum # even is packed into bits 39 to 30 while Final Sum # odd is packed into bits 19 to 0. As of this date 03/10/09 bits 63..40 are set to zeroes.

#### 3.6 **Disable FADC**

An FADC can be Data from FADC can be disabled by writing to Configuration register via I-square-C interface. When disabled, the code does not wait for data from that FADC. The bits corresponded to that FADC are zero in the summing process.

### 3.7 **Processing Delay**

The number of clock from Datrdy (from VLX50) going high to FIFO empty going low is 8 clock (32 nS). Adder stages take 11 clock (44 ns).

### 3.8 Threshold

A register accessed through I-Square-C provides a threshold for the final sum . When the final sum is above the threshold, Trigger Output at the front panel is active high. If the History Buffer described below is armed, 256 additional sums are stored and ready to be read out.

### 3.9 **History Buffer**

The History Buffer stores 512 Microscope or Hodoscope HitBits pattern that go to the SSP. The History continues to store 255 samples. When it is trigger, it will store 255 more samples and then stop. It is trigger when a bit that is enable by U24 registers 8 and 9 is a one. A HitBit is enable to trigger the History Buffer when the corresponding bit in U24 Register 8 and 9 is a one. It is controlled and read out via I-Square-C. The steps to use the history buffer are as follow:

- Host sets ARM to one.

- Host sets ARM to zero.

- After 256 HitBits are stored in Memory, waiting for HitBit Pattern to match U24 Regiser 8 and 9. Continues storing Final Sum

- When Final Sum reach threshold. 256 more values are stored.

- Stops storing.

- Host polled for DataReady for high.

- Read as much values as host wanted. Data read back is auto increment.

• Host sets ARM to clear DataReady.

### 3.10 **Automate Testing.**

The integrity of the data transfer from FADC250 to CTP can be verified. When bit 1 of MGT\_CTRL register in FADC250 is 0, counting sequences (0,1,2,3,4, etc.). The CTP adds the data from all enable FADC250 and compare to expected sum. For example, if 8 FADC250 are enable, the expected Sum are 0, 8, 16, 24, 32, etc. If at any time the actual Sum and the expected Sum are not equaled, ERROR\_LATCH\_FS variable goes high and stay high until Sync goes high. To use this feature:

- Reset control mgt bit 3 so the FLASH is sending SUM to CTP

- Execute all steps except the last step (10.11) in "Steps to Align Data from FLASH". Leave FADC250 control mgt bit 1 a zero...

- Wait for however long the testing is desire.

- Read Is2 status register bit ERROR\_LATCH\_FS. If it is zero the data from the FADC250 are OK.

- Make bit 1 of of MGT\_CTRL register in FADC250 one. ERROR\_LATCH\_FS should be one because data from FADC250 is not counting sequence.

### 3.11 **Xilinx System Monitor**

Xilinx System Monitor feature that indicates the die temperature and VCCINT and VCCAUX Supply is included. The data is mapped into register file that can be read back through I-Square-C. The host has to convert binary data to temperature and voltage (See Xilinx UG192).

### 4.0 I-Square-C interface

Data is written to and read from the CTP serially from VXS P1 connector. The serial interface consists of an input clock bit and a bidirectional data bit that connected to all three FPGA. The FPGA de-serializes the data bits and listens for its address. The FPGA have non-overlapping address and responses when it is addressed. Each Register is 16 bits wide.

### **5.0 Total Processing Delay**

It takes a total of 27 clocks (8 from VLX50, 8 to receive data from VLX50, 11 from adder stages) from the time data arrived from the slowest FADC to produce the first Final Sum.

### **6.0 LED**

```

LED(0) <= HEART_BEAT_250;

LED(1) <= HEART_BEAT_200;

LED(2) <= ABOVE_THREDSHOLD_BUF_Q(0); --; Heartbeat 200

LED(3) <= indicate all MGT lanes and all MGT Channels of U24 are OK.

LED(4) <= HEART_BEAT_INIT;

LED(5) <= Indicate there is not Fiber Fault and Fiber is ready---

```

```

LED(6) \le '1';

```

### 7.0 SD Test Code

- 7.1 Count Rising Edge of Sync, Trig1, Trig2 from SD.

- 7.2 Measure Clock from SD (should be 250 MHz)

- 7.3 Connect SD\_IN\_SPARE 0 to SD\_OUT\_SPARE 0

- 7.4 Connect SD IN SPARE 1 to SD OUT SPARE 1

### 8.0 Configuring FPGA from I-SQUARE-C Bus

This feature allows FPGA configuration data to be downloaded from I-Square-C and stored into one of the three Configuration ROMs which are AT45DB642. U1, U3, and U24 have a separate Configuration ROM. This feature also allows rebooting (reloading) the FPGA. CTPV2 FpgaConfigExamples.C shows the routines. When writing C code the first time, it is recommend to write and verify the C Code for the Read FPGA Config Data from ROM to SRAM. This is to minimize the mistake of continuously Erasing and Programming the ROM. ROM is rated for 100,000 erases/writes cycles.

- 8.1 The overall steps are (details steps follow):

- 8.1.1 Host issues Erase Commands to U1 to erase U1, U3, or U24.

- 8.1.2 Host downloads the entire FPGA Configuration Data (MCS file) for U1, U3, or U24's Configuration ROM to U1. U1 stores the data on onboard SRAM

- 8.1.3 Host read back data from SRAM for verification.

- 8.1.4 Host issues command to U1 to store data from SRAM into U1, U3, or U24's Configuration. ROM. Host wait until U1 finishes storing data to ROM

- 8.1.5 Host issues command to U1 to read Configuration ROM of U1, U3, or U24 to SRAM. Host wait for U1 to finish reading

- 8.1.6 Host reads data from SRAM and verifies that data is corrected. If data does not match the MCS file, host can redo steps 8.1.1 to 8.1.6.

- 8.1.7 If desire (not necessary) host can repeat steps 8.1.1 to 8.1.6 for the remaining FPGA.

- 8.1.8 Host issues command to U3 to reboot ALL FPGA. There is no command to reboot individual FPGA.

- 8.2 Erase Command (See Register File) Make sure U1 Register 17 (Status 2) bit 15 is a one:

### 8.2.1 For U1

- 8.2.1.1 Initialize variable Config\_ROM\_Block\_Number\_to\_Erase to zero.

- 8.2.1.2 Write Config\_ROM\_Block\_Number\_to\_Erase to U1 Register 7 bit 9..0

- 8.2.1.3 Write the following bits values to U1 Register 6 to start Erase U1 Rom

$$8.2.1.3.1$$

$10..9 = 01$   $8.2.1.3.2$   $8 = 1$   $8.2.1.3.3$   $7 = 0$

$$8.2.1.3.4$$

$6..3 = 1001$

- 8.2.1.4 Poll U1 Register 17 (Status 2) bit 15 until it is a one. Fpga Config is done erasing Config\_ROM\_Block\_Number\_to\_Erase.

- 8.2.1.5 Write the following bits values to U1 Register 6 to ready for next command

$$8.2.1.5.1$$

$10..9 = 01$

$8.2.1.5.2$   $8 = 0$

$8.2.1.5.3$   $7 = 0$

$8.2.1.5.4$   $6..3 = 1001$

- 8.2.1.6 Increment Config\_ROM\_Block\_Number\_to\_Erase

- 8.2.1.7 **WAIT** for 220 milliSecond. This is the time the ROM takes to Erase one block.

- 8.2.1.8 Repeat 8.2.1.2 to 8.2.1.6 for Config\_ROM\_Block\_Number\_to\_Erase from 1 to 1023 to erase all 1024 ROM's Blocks.

### 8.2.2 For U3

- 8.2.2.1 Initialize variable Config\_ROM\_Block\_Number\_to\_Erase to zero.

- 8.2.2.2 Write Config\_ROM\_Block\_Number\_to\_Erase to U1 Register 7 bit 9..0

- 8.2.2.3 Write the following bits values to U1 Register 6 to start Erase U1 Rom

$$8.2.2.3.1$$

$10..9 = 10$

$8.2.2.3.2$   $8 = 1$

$8.2.2.3.3$   $7 = 0$

$8.2.2.3.4$   $6..3 = 1010$

- 8.2.2.4 Poll U1 Register 17 (Status 2) bit 15 until it is a one. Fpga Config is done erasing Config\_ROM\_Block\_Number\_to\_Erase.

- 8.2.2.5 Write the following bits values to U1 Register 6 to ready for next command

$$8.2.2.5.1$$

$10..9 = 10$

$8.2.2.5.2$   $8 = 0$

$8.2.2.5.3$   $7 = 0$

$8.2.2.5.4$   $6..3 = 1010$

- 8.2.2.6 Increment Config\_ROM\_Block\_Number\_to\_Erase.

- 8.2.2.7 Repeat 8.2.2.2 to 8.2.2.6 for

Config\_ROM\_Block\_Number\_to\_Erase from 1 to 1023 to erase all 1024 ROM's Blocks.

### 8.2.3 For U24

- 8.2.3.1 Initialize variable Config\_ROM\_Block\_Number\_to\_Erase to zero

- 8.2.3.2 Write Config\_ROM\_Block\_Number\_to\_Erase to U1 Register 7 bit 9..0

- 8.2.3.3 Write the following bits values to U1 Register 6 to start Erase U1 Rom

$$8.2.3.3.2$$

$8 = 1$

$8.2.3.3.3$   $7 = 0$

$8.2.3.3.4$   $6..3 = 1011$

- 8.2.3.4 Poll U1 Register 17 (Status 2) bit 15 until it is a one. Fpga Config is done erasing Config\_ROM\_Block\_Number\_to\_Erase.

- 8.2.3.5 Write the following bits values to U1 Register 6 to ready for next command

$$8.2.3.5.1$$

$10..9 = 11$

$8.2.3.5.2$   $8 = 0$

$8.2.3.5.3$   $7 = 0$

$8.2.3.5.4$   $6..3 = 1011$

- 8.2.3.6 Increment Config\_ROM\_Block\_Number\_to\_Erase

- 8.2.3.7 Repeat 8.2.3.2 to 8.2.3.6 for

Config\_ROM\_Block\_Number\_to\_Erase from 1 to 1023 to erase all 1024 ROM's Blocks.

8.3 Download FPGA Config Data to SRAM (See Register File) Make sure U1 Register 17 (Status 2) bit 15 is a one:

### 8.3.1 For U1, U3, U24

8.3.1.1 Write the following bits values to U1 Register 6 to select SRAM for writing.

$$8.3.1.1.1$$

$10..9 = 00$

$8.3.1.1.2$   $8 = 0$

$8.3.1.1.3$   $7 = 1$

$8.3.1.1.4$   $6..3 = 0000$

- 8.3.1.2 Initialize 22 bits variable SRAM Address to 0

- 8.3.1.3 Read 2 bytes from Xilinx MCS data bytes to variable SRAM\_DATA. The first byte read go to bits 15..8 and the second byte read go to bits 7..0.

- 8.3.1.4 Write SRAM\_DATA to U1 Register 8

- 8.3.1.5 Write bits 15..0 of SRAM Address to U1 Register 9.

- 8.3.1.6 Write the following bits values to U1 Register 10 to write SRAM Data to SRAM Address.

8.3.1.7 Write the following bits values to U1 Register 10 to ready for the next write.

- 8.3.1.8 Increment SRAM Address

- 8.3.1.9 Repeat 8.3.1.2 to 8.3.1.8 for remaining bytes in MCS file

- 8.4 ReadBack FPGA Config Data to SRAM (See Register File) Make sure U1 Register 17 (Status 2) bit 15 is a one:

### 8.4.1 For U1, U3, U24

8.4.1.1 Write the following bits values to U1 Register 6 to select SRAM for reading.

$$8.4.1.1.1$$

$10..9 = 00$

$8.4.1.1.2$   $8 = 0$

$8.4.1.1.3$   $7 = 1$

$8.4.1.1.4$   $6..3 = 0000$

- 8.4.1.2 Initialize 22 bits variable SRAM Address to 0

- 8.4.1.3 Read 2 bytes from Xilinx MCS data bytes to variable SRAM\_DATA. The first byte read go to bits 15..8 and the second byte read go to bits 7..0.

- 8.4.1.4 Write bits 15..0 of SRAM\_Address to U1 Register 9.

- 8.4.1.5 Write the following bits values to U1 Register 10 to read SRAM\_Data from SRAM\_Address.

- 8.4.1.6 Poll U1 Register 17 (Status 2) bit 15 until it is a one.

- 8.4.1.7 Write the following bits values to U1 Register 10 to ready for the next write.

- 8.4.1.8 Read Data From SRAM at U1 Register 11

- 8.4.1.9 Compare Data From SRAM (8.4.1.8) to SRAM\_DATA (8.4.1.3)

- 8.4.1.10 Increment SRAM Address

- 8.4.1.11 Repeat 8.3.1.2 to 8.3.1.8 for remaining bytes in MCS file

- 8.5 Program FPGA Config Data from SRAM to ROM (See Register File) Make sure U1 Register 17 (Status 2) bit 15 is a one:

### 8.5.1 For U1

8.5.1.1 Write the following bits values to U1 Register 6 to start program FPGA Config Data from SRAM to ROM

$$8.5.1.1.1$$

$10..9 = 01$

$8.5.1.1.2$   $8 = 1$

$8.5.1.1.3$   $7 = 0$

$8.5.1.1.4$   $6..3 = 0000$

- 8.5.1.2 Poll U1 Register 17 (Status 2) bit 15 until it is a one. One indicates that Fpga Config is done storing Config Data to ROM-Opcodes 0,1,2 can only be issued at 10 minutes interval to prevent exceeding the ROM (AT45DB642) maximum write of 100,000 times.

- 8.5.1.3 Write the following bits values to U1 Register 6 to ready for next command

$$8.5.1.3.1$$

$10..9 = 01$

$8.5.1.3.2$   $8 = 0$

$8.5.1.3.3$   $7 = 0$

$8.5.1.3.4$   $6..3 = 0000$

#### 8.5.2 For U3

8.5.2.1 Write the following bits values to U1 Register 6 to start program FPGA Config Data from SRAM to ROM

8.5.2.1.1 10..9 = 10 8.5.2.1.2 8 = 1 8.5.2.1.3 7 = 08.5.2.1.4 6..3 = 0001

- 8.5.2.2 Poll U1 Register 17 (Status 2) bit 15 until it is a one. One indicates that Fpga Config is done storing Config Data to ROM. Opcodes 0,1,2 can only be issued at 10 minutes interval to prevent exceeding the ROM (AT45DB642) maximum write of 100,000 times.

- 8.5.2.3 Write the following bits values to U1 Register 6 to ready for next command

8.5.2.3.1 10..9 = 10 8.5.2.3.2 8 = 0 8.5.2.3.3 7 = 08.5.2.3.4 6..3 = 0001

#### 8.5.3 For U24

8.5.3.1 Write the following bits values to U1 Register 6 to start program FPGA Config Data from SRAM to ROM

8.5.3.1.1 10..9 = 11 8.5.3.1.2 8 = 1 8.5.3.1.3 7 = 08.5.3.1.4 6..3 = 0010

- 8.5.3.2 Poll U1 Register 17 (Status 2) bit 15 until it is a one. One indicates that Fpga Config is done storing Config Data to ROM. Opcodes 0,1,2 can only be issued at 10 minutes interval to prevent exceeding the ROM (AT45DB642) maximum write of 100,000 times.

- 8.5.3.3 Write the following bits values to U1 Register 6 to ready for next command

8.5.3.3.1 10..9 = 11 8.5.3.3.2 8 = 0 8.5.3.3.3 7 = 08.5.3.3.4 6..3 =**0011**

8.6 Read FPGA Config Data from ROM to SRAM (See Register File) Make sure U1 Register 17 (Status 2) bit 15 is a one:

#### 8.6.1 For U1

8.6.1.1 Write the following bits values to U1 Register 6 to start program FPGA Config Data from SRAM to ROM

8.6.1.1.1 10..9 = 01 8.6.1.1.2 8 = 1 8.6.1.1.3 7 = 08.6.1.1.4 6..3 =**0011**

- 8.6.1.2 Poll U1 Register 17 (Status 2) bit 15 until it is a one. One indicates that Fpga Config is done reading Config Data from ROM and storing to SRAM.

- 8.6.1.3 Write the following bits values to U1 Register 6 to ready for next command

```

8.6.1.3.1 10..9 = 01

8.6.1.3.2 8 = 0

8.6.1.3.3 7 = 0

8.6.1.3.4 6..3 = 0011

```

- 8.6.1.4 Follow steps under ReadBack FPGA Config Data to SRAM to verify that data is the ROM match MCS file.

- 8.7 Rebooting FPGA (Reloading FPGA with Config Data from ROM):

- 8.7.1 Before issuing this command, make sure the Config Data for U1 is corrected because U1 code contains the Configuration algorithm. If wrong code is loaded into U1, a local reload (with a lab top) has to be done. This command will reboot all three FPGA

#### 8.7.2 For all FPGA

8.7.2.1 Write the following bits values to U3 Register 7 to reboot all FPGA

### 9.0 Board Serial Number

- 9.1 The board serial number is stored in Serial ROM (SROM) in ASCII format. The board serial number is CTPV2xxx where xxx is (ASCII) number of the board. The serial ROM is connected to U3.

- 9.2 Steps to read the board serial number

- 9.2.1 Set SROM Address variable to zero.

- 9.2.2 Write SROM Address variable to U3 Config 2 bits 9..0

- 9.2.3 Set Bit 15 of **U3** Config 2 to read one byte at SROM Address

- 9.2.4 Reset Bit 15 of **U3** Config 2.

- 9.2.5 Poll bit 15 of U3 Status 3 for Read Done

- 9.2.6 Read byte (in ASCII) from **U3** Status 3 bits 7..0.

- 9.2.7 ReSet Bit 15 of **U3** Config 2.

- 9.2.8 Increment SROM Address.

- 9.2.9 Repeat 9.2.1 to 9.2.7 for the remain Bytes.

### 10.0 Steps to Align Data from FLASH Boards

- 10.1 **Set** control\_mgt bit 0. This Reset MGT Channels.

- 10.2 **Reset** control\_mgt bit 0. Wait 1 uS for all channels to come up

- 10.3 **ReSet** control\_mgt bit 1. This instruct FADC to send Counting Sequence to CTP

- 10.4 **Set** control\_mgt register Bit 2 of all FLASH board. This allows FLASH board(s) to send alignment sequence to CTP.

- 10.5 **Set** Config1 register Bit 3 of U1, U3, and U24 of CTPV2 board. This allows U1, U3, and U24 to execute alignment routine.

- 10.6 Bring SYNC line to high to all boards for at least 1uS.

- 10.7 Bring SYNC line back to low.

- 10.8 **Reset** control\_mgt register Bit 2 of all FLASH board. This disables FLASH from sending alignment sequence at SYNC.

- 10.9 **Reset** Config1 register Bit 3 of U1, U3, and U24. This disables U1, U3, and U24 from executing alignment routine at SYNC.

- 10.10 Poll Status 1 Bit 9 of U24 for a one. This indicates the alignment is successful. If this bit does not go high after 200nS, there is something wrong.

- 10.11 **Set** control\_mgt bit 1. This instruct FADC to send data from ADC FPGA to CTP

### 11.0 Crate ID

11.1 The 16-bits Crate ID is to identify the location of the crate in a system. It is programmable by the user and sent to the SSP on the lower sixteen bits of the first 64-bits word

### 12.0 Microscope Trigger Algorithm:

- 12.1 This implement the requirement outlined in "hit\_pattern\_description.doc" by Alex Somov

- 12.2 Data from FLASH250 must be HitBits.

- 12.3 The HitBits are grouped in group of 4. There are 29 groups. The mapping is shown in Figure 5.

- 12.4 HitBits are rising edge detected. When one of the HitBit in a group is a high, a Hit Window is open and any remaining bits that go high during this Window time are part of this time.

- 12.5 At the end of Hit Window, a one clock pulse is generated for that group and is sent to the SSP. Hit Window width is 4-bits programmable by the user.

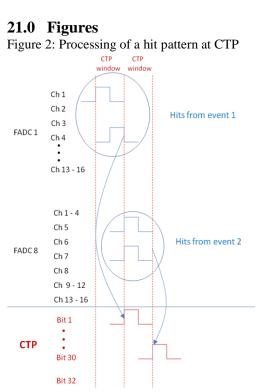

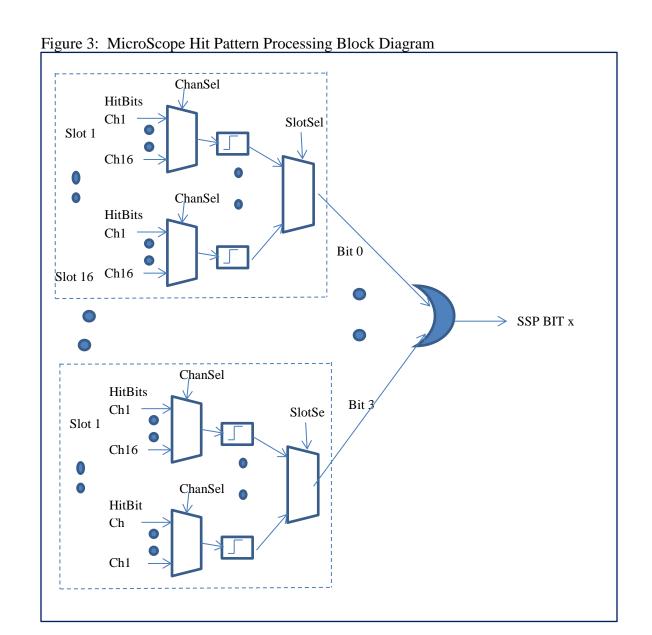

- 12.6 Figure 2 shows the timing for HitBits. Figure 3 shows the block diagram for the Microscope processing algorithm.

- 12.7 Table 1 shows the FLASH slot and ADC channels to Microscope SSP bits mapping.

- 12.8 Lemo Trig Mont Out is the Oring of all SSP bits.

## 13.0 HodoScope Trigger Algorithm:

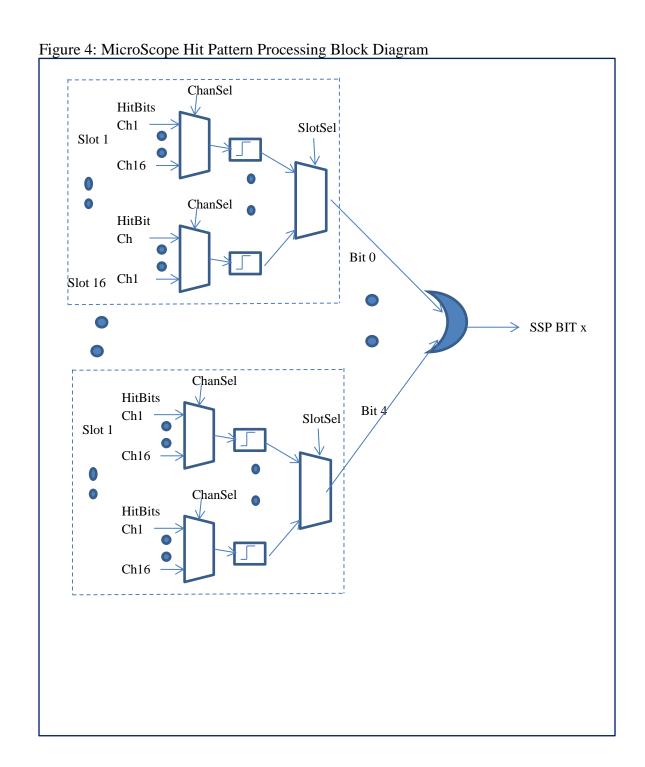

- 13.1 HodoScope processing is the same as MicroScope with the exception that the OR is grouped of 5 ADC channels.

- 13.2 Figure 4 shows the block diagram for the Hodoscope processing algorithm.

- Table 2 shows the FLASH slot and ADC channels to Microscope SSP bits mapping.

- 13.4 Lemo Trig Mont Out is the Oring of all SSP bits.

- 13.5

### 14.0 Selecting MicroScope or HodoScope Trigger Algorithm:

14.1 When Bit 11 of Config3 is a zero, HitBit 29..0 outputs of MicroScope Processing is sent to SSP

14.2 When Bit 11 of Config3 is a one, HitBit 23..0 outputs of HodoScope Processing is sent to SSP14.3

# 15.0 Register File

**I-Square-C Address Mapping**

| _          | ddress Mappi |     | Eurotion                                  |

|------------|--------------|-----|-------------------------------------------|

| I-Square-C | I-Square-C   | R/W | Function                                  |

| Board      | Sub          |     |                                           |

| Address    | Address      |     | G A                                       |

| 0 (U1)     | 0            | R   | Status 0                                  |

|            |              |     | 15: Payload 13 MGT Channel Up             |

|            |              |     | 14: Payload 11 MGT Channel Up             |

|            |              |     | 13: Payload 9 MGT Channel Up              |

|            |              |     | 12: Payload 7 MGT Channel Up              |

|            |              |     | 11: Undefine                              |

|            |              |     | 10: Undefine                              |

|            |              |     | 9: Payload 15 MGT Lane 1 Up               |

|            |              |     | 8: Payload 15 MGT Lane 0 Up               |

|            |              |     | 7: Payload 13 MGT Lane 1 Up               |

|            |              |     | 6: Payload 13 MGT Lane 0 Up               |

|            |              |     | 5: Payload 11 MGT Lane 1 Up               |

|            |              |     | 4: Payload 11 MGT Lane 0 Up               |

|            |              |     | 3: Payload 9 MGT Lane 1 Up                |

|            |              |     | 2: Payload 9 MGT Lane 0 Up                |

|            |              |     | 1: Payload 7 MGT Lane 1 Up                |

|            |              |     | 0: Payload 7 MGT Lane 0 Up                |

|            | 1            | R   | Status 1                                  |

|            |              |     | 152: Undefine                             |

|            |              |     | 1: Payload 15,13,11,9,7 MGT Channels Up   |

|            |              |     | 0: Payload 15 MGT Channel Up              |

|            | 2            | R/W | Config 0                                  |

|            |              |     | 6: Enable Payload 7                       |

|            |              |     | 8: Enable Payload 9                       |

|            |              |     | 10: Enable Payload 11                     |

|            |              |     | 12: Enable Payload 13                     |

|            |              |     | 14: Enable Payload 15                     |

|            | 3            | R/W | Config 1                                  |

|            |              |     | 3: Enable Alignment of Data from FLASH on |

|            |              |     | falling edge of Sync                      |

|            |              |     | 1: Init All MGT                           |

|            | 4            | R   | Die Temperature                           |

|            | 5            | R   | Vint                                      |

|            | 6            | R/W | Config 2                                  |

|            |              |     | Fpga Configuration:                       |

|            |              |     | 109 = 1 -> Sel U1 for configuration       |

|            |              |     | = 2 -> Sel U3 for configuration           |

|            |              |     | = 3 -> Sel U24 for configuration          |

|            |              |     | 8 = Rising edge Execute Opcode            |

|            |              |     | 7 = 1 Select SRAM for writing             |

|         | 1     | I   |                                                |

|---------|-------|-----|------------------------------------------------|

|         |       |     | 63 = 0 -> PROGRAM_DATA_U1.                     |

|         |       |     | 1 -> PROGRAM_DATA_U3.                          |

|         |       |     | 2 -> PROGRAM_DATA_U24.                         |

|         |       |     | 3 -> READ_DATA_U1.                             |

|         |       |     | 4 -> <b>READ_DATA_U3</b> .                     |

|         |       |     | 5 -> <b>READ_DATA_U24.</b>                     |

|         |       |     | 6 -> READ_EPROM_ID_U1.                         |

|         |       |     | 7 -> READ_EPROM_ID_U3.                         |

|         |       |     | 8 -> READ_EPROM_ID_U24.                        |

|         |       |     | 9 -> ERASE_EPROM_U1                            |

|         |       |     | A -> ERASE_EPROM_U3                            |

|         |       |     | B -> ERASE_EPROM_U24                           |

|         |       |     | C ->                                           |

|         |       |     | D ->                                           |

|         |       |     | E ->                                           |

|         |       |     | F ->                                           |

|         |       |     | 20 = undefine                                  |

|         | 7     | R/W | Config 3                                       |

|         |       |     | Fpga Configuration:                            |

|         |       |     | 90 -> Config ROM Block Number to               |

|         |       |     | Erase                                          |

|         | 8     | R/W | Config 4                                       |

|         |       |     | Sram Data                                      |

|         |       |     | 150 = Data to be written to SRAM               |

|         | 9     | R/W | Config 5                                       |

|         |       |     | Sram Address                                   |

|         |       |     | 150 = Sram Address 150                         |

|         | 10    | R/W | Config 6                                       |

|         |       |     | Sram Address, R/W                              |

|         |       |     | 15 = Rising edge write Sram Data to Sram       |

|         |       |     | Address                                        |

|         |       |     | 14 = Rising edge read Data at Sram Address.    |

|         |       |     | Data is available at Data From Sram            |

|         |       |     | 136 = undefined                                |

|         |       |     | 50 = Sram Address 2116                         |

|         | 11    | R   | Status 3                                       |

|         | 11    | 1   | Data From Sram                                 |

|         |       |     | 150 = Data read from Sram Address              |

|         | 12-16 |     | Undefine                                       |

|         |       | R   | Status 2                                       |

|         | 17    | K   |                                                |

|         |       |     | 15: 1 -> Fpga Config is Idle. Ready for opcode |

|         |       |     | 14 O. E                                        |

|         |       |     | 140: Firmware Version                          |

|         |       |     |                                                |

| 1 (775) |       | -   |                                                |

| 1 (U3)  | 0     | R   | Status 0                                       |

|          | 1      | 15. D. L. 114 MOTE OF 137                                 |

|----------|--------|-----------------------------------------------------------|

|          |        | 15: Payload 14 MGT Channel Up                             |

|          |        | 14: Payload 12 MGT Channel Up                             |

|          |        | 13: Payload 10 MGT Channel Up                             |

|          |        | 12: Payload 8 MGT Channel Up                              |

|          |        | 11: Undefine                                              |

|          |        | 10: Undefine                                              |

|          |        | 9: Payload 14 MGT Lane 1 Up                               |

|          |        | 8: Payload 14 MGT Lane 0 Up                               |

|          |        | 7: Payload 12 MGT Lane 1 Up                               |

|          |        | 6: Payload 12 MGT Lane 0 Up                               |

|          |        | 5: Payload 10 MGT Lane 1 Up                               |

|          |        | 4: Payload 10 MGT Lane 0 Up                               |

|          |        | 3: Payload 8 MGT Lane 1 Up                                |

|          |        | 2: Payload 8 MGT Lane 0 Up                                |

|          |        | 1: Payload 6 MGT Lane 1 Up                                |

| 1        | D      | 0: Payload 6 MGT Lane 0 Up                                |

| 1        | R      | Status 1                                                  |

|          |        | 152: Undefine<br>1: Payload 16,14,12,10,8 MGT Channels Up |

|          |        | 1 1 1                                                     |

| 2        | R/W    | 0: Payload 16 MGT Channel Up<br>Config 0                  |

| <u> </u> | IX/ VV | 7: Enable Payload 8                                       |

|          |        | 9: Enable Payload 8                                       |

|          |        | 11: Enable Payload 12                                     |

|          |        | 13: Enable Payload 14                                     |

|          |        | 15: Enable Payload 16                                     |

| 3        | R/W    | Config 1                                                  |

|          |        | 3: Enable Alignment of Data from FLASH on                 |

|          |        | falling edge of Sync                                      |

|          |        | 1: Init All MGT                                           |

| 4        | R      | Die Temperature                                           |

| 5        | R      | Vint                                                      |

| 6        | R/W    | Config 2                                                  |

|          |        | SROM                                                      |

|          |        | 15: Rising edge read byte from SROM Address               |

|          |        | 90: SROM Address                                          |

| 7        | R/W    | Config 3                                                  |

|          |        | 20 = 5 -> reboot ALL FPGA                                 |

| 8-10     |        | Undefine                                                  |

| 11       | R      | Status 3                                                  |

|          |        | Data From Serial ROM                                      |

|          |        | 15: ASCII Data from SROM Valid                            |

|          |        | 70: ASCII Data read from SROM Address                     |

| 12=16    |        | Undefine                                                  |

| 17       | R      | Status 2                                                  |

|          |        | 15: Undefine                                              |

| <br>     |        |                                                           |

|         |   |     | 140: Firmwarw Version                     |  |

|---------|---|-----|-------------------------------------------|--|

|         |   |     |                                           |  |

|         |   |     |                                           |  |

| 2 (U24) | 0 | R   | Status 0                                  |  |

| 2 (024) |   |     | 15: Payload 2 MGT Channel Up              |  |

|         |   |     | 14: Payload 5 MGT Channel Up              |  |

|         |   |     | 13: Payload 1 MGT Channel Up              |  |

|         |   |     | 12: Payload 3 MGT Channel Up              |  |

|         |   |     | 11: Payload 6 MGT Lane 1 Up               |  |

|         |   |     | 10: Payload 6 MGT Lane 0 Up               |  |

|         |   |     | 9: Payload 4 MGT Lane 1 Up                |  |

|         |   |     | 8: Payload 4 MGT Lane 0 Up                |  |

|         |   |     | 7: Payload 2 MGT Lane 1 Up                |  |

|         |   |     | 6: Payload 2 MGT Lane 0 Up                |  |

|         |   |     | 5: Payload 5 MGT Lane 1 Up                |  |

|         |   |     | 4: Payload 5 MGT Lane 0 Up                |  |

|         |   |     | 3: Payload 1 MGT Lane 1 Up                |  |

|         |   |     | 1                                         |  |

|         |   |     | 2: Payload 1 MGT Lane 0 Up                |  |

|         |   |     | 1: Payload 3 MGT Lane 1 Up                |  |

|         | 1 | D   | 0: Payload 3 MGT Lane 0 Up                |  |

|         | 1 | R   | Status 1                                  |  |

|         |   |     | 159: Undefine                             |  |

|         |   |     | 9: DataAlign Done                         |  |

|         |   |     | 8: Error in Sum in Test Mode              |  |

|         |   |     | 7: Fiber Channel Ready                    |  |

|         |   |     | 6: Fiber Lane Remote Up                   |  |

|         |   |     | 5: Fiber Lane Byte Align                  |  |

|         |   |     | 4: Fiber Lane Channel Align               |  |

|         |   |     | 3: History Data REady                     |  |

|         |   |     | 2: Payload 6 MGT Channel Up               |  |

|         |   |     | 1: Payload 1,2,3,4,5,6 MGT Channels Up    |  |

|         |   |     | 0: Payload 4 MGT Channel Up               |  |

|         | 2 | R/W | Config 0                                  |  |

|         |   |     | 0: Enable Payload 1                       |  |

|         |   |     | 1: Enable Payload 2                       |  |

|         |   |     | 2: Enable Payload 3                       |  |

|         |   |     | 3: Enable Payload 4                       |  |

|         |   |     | 4: Enable Payload 5                       |  |

|         |   |     | 5: Enable Payload 6                       |  |

|         | 3 | R/W | Config 1                                  |  |

|         |   |     | 153:                                      |  |

|         |   |     | 3: Enable Alignment of Data from FLASH on |  |

|         |   |     | falling edge of Sync                      |  |

|         |   |     | 2: Reset Fiber MGT                        |  |

|         |   |     | 1: Init All MGT                           |  |

|         |   |     | 0: History Arm                            |  |

|         |   |     | v. mistory farm                           |  |

| 4  | R      | U24 FX100T Die Temperature                  |

|----|--------|---------------------------------------------|

| 5  | R      | U24 FX100T Vint                             |

| 6  | R/W    | Undefine                                    |

| 7  | R/W    | Undefine                                    |

| 8  | R/W    | History Buffer Trigger Enable Bit 150       |

| 9  | R/W    | History Buffer Trigger Enable Bit 3116      |

| 10 | R      | History Buffer Data LSB                     |

| 11 | R      | History Buffer Data MSB                     |

| 12 | R/W    | SD Test Control Register                    |

| 12 | 10, 11 | Bits:                                       |

|    |        | 0 : Reset SYNC Count Reg 14                 |

|    |        | 1 : Reset TRIG 1 Count Reg 15               |

|    |        | 2: Reset TRIG 2 Count Reg 16                |

| 13 | R      | SD Clock Frequency (MHz)                    |

|    |        | Bits (7 0) : Clock 250 Count (Should be 250 |

|    |        | +/- 2)                                      |

| 14 | R      | Count Rising Edge of Sync From SD           |

|    |        | Bits (15:0) Count Rising Edge of SYNC from  |

|    |        | SD. Sync must be high for at least 30 nS    |

| 15 | R      | Count Rising Edge of Trig1 from SD          |

|    |        | Bits (15:0) Count Rising Edge of TRIG1 from |

|    |        | SD. Sync must be high for at least 30 nS    |

| 16 | R      | Count Rising Edge of Trig2 from SD          |

|    |        | Bits (15:0) Count Rising Edge of TRIG2 from |

|    |        | SD. Sync must be high for at least 30 nS    |

| 17 | R      | Status 2:                                   |

|    |        | 15: Undefine                                |

|    |        | 140: Firmware Version                       |

| 18 | R/W    | Config 2: Crate ID                          |

| 19 | R/W    | Config 3:                                   |

|    |        | 1512 →                                      |

|    |        | 11 → 0 : Select MicroScope                  |

|    |        | 1: Select HodoScope                         |

|    |        | 107 → Micro and Hodo Scope Coincident       |

|    |        | Window Width                                |

|    |        | 60 →                                        |

| 20 | R/W    | Config 4:                                   |

|    |        | 150 → BCAL Threshold                        |

The history data advance after Data MSB is read. Hence read LSB then MSB.

16.0: Channel Number to PayLoad Mapping:

| FPGA | FADC #  | Payload |

|------|---------|---------|

|      | Channel | -       |

| U24  | 0       | 3       |

|      | 1       | 1       |

|      | 2       | 5       |

|      | 3       | 2       |

|      | 4       | 4       |

|      | 5       | 6       |

|      |         |         |

| U1   | 0       | 7       |

|      | 1       | 9       |

|      | 2       | 11      |

|      | 3       | 13      |

|      | 4       | 15      |

|      |         |         |

| U3   | 0       | 8       |

|      | 1       | 10      |

|      | 2       | 12      |

|      | 3       | 14      |

|      | 4       | 16      |

|      |         |         |

|      |         |         |

Temperature\_C = ((float)TempRegValue \* 503.975/1024) - 273.15;

17.0 Table 1 : FLASH Slots and ADC channels to MicroScope SSP Bit Mapping

| 17.0 Tai |          | DII DIUL | s and ADC channels to | •            |

|----------|----------|----------|-----------------------|--------------|

|          |          |          |                       | ADC          |

| SSP Bit  | 4 bit OR | Slot#    | MicroScope Chan#      | CHANNEL      |

| 0        |          | 3        | 1,2,3,4               | 0,1,2,3      |

| 1        |          | 3        | 5,6,7,8               | 4,5,6,12     |

| 2        |          | 3,(4)    | 9,10,11,12            | 13,14,15,(0) |

| 3        |          | 4        | 13,14,15,16           | 1,2,3,4      |

| 4        |          | 4        | 17,18,19,20           | 5,6,7,8      |

| 5        |          | 4        | 21,22,23,24           | 9,10,11,12   |

| 6        |          | 4,(5)    | 25,26,27,28           | 13,(3,4,5)   |

| 7        |          | 5        | 29,30,31,32           | 6,7,8,9      |

| 8        |          | 5        | 33,34,35,36           | 10,11,12,13  |

| 9        |          | 5,(6)    | 37,38,39,40           | 14,15,(0,1)  |

| 10       |          | 6        | 41,42,43,44           | 2,3,4,5      |

| 11       |          | 6        | 45,46,47,48           | 6,7,8,9      |

| 12       |          | 6        | 49,50,51,52           | 10,11,12,13  |

| 13       |          | 6,(7)    | 53,54,55,56           | 14,15,(0,1)  |

| 14       |          | 7        | 57,58,59,60           | 2,3,4,5      |

| 15       |          | 7        | 61,62,63,64           | 6,7,8,9      |

| 16       |          | 7        | 65,66,67,68           | 10,11,12,13  |

| 17       |          | 7,(8)    | 69,70,71,72           | 14,15,(0,1)  |

| 18       |          | 8        | 73,74,75,76           | 2,3,4,5      |

| 19       |          | 8        | 77,78,79,80           | 6,7,8,14     |

| 20       |          | 8,(9)    | 81,82,83,84           | 15,(0,1,2)   |

| 21       |          | 9        | 85,86,87,88           | 3,4,5,6      |

| 22       |          | 9        | 89,90,91,92           | 7,8,9,10     |

| 23       |          | 9        | 93,94,95,96           | 11,12,13,14  |

| 24       |          | 9,(10)   | 97,98,99,100          | 15,(5,6,7)   |

| 25       |          | 9        | Undefined             |              |

| 26       |          | 9        | Undefined             |              |

| 27       |          | 9        | Undefined             |              |

| 28       |          | 10       | Undefined             |              |

| 29       |          | 10       | Undefined             |              |

| 30       |          |          | Undefined             |              |

| 31       |          |          | Undefined             |              |

18.0 Table 2: FLASH Slots and ADC channels to HodoScope SSP Bit Mapping

| 18.0 Tab | le 2 : FLA | SH Slots | and ADC channels to | HodoScope SSP Bit Maj |

|----------|------------|----------|---------------------|-----------------------|

| SSP Bit  | 5 bit OR   | Slot#    | Chan#               | ADC CHANNEL           |

| 0        |            | 3        | 1,2,3,4,5           | 0,1,2,3,4             |

| 1        |            | 3        | 6,7,8,9,10          | 5.6.7.8.9             |

| 2        |            | 3        | 11,12,13,14,15      | 10,11,12,13,14        |

| 3        |            | 3        | 16                  | 15                    |

| 3        |            | 4        | 17,18,19,20         | 0,1,2,3               |

| 4        |            | 4        | 21,22,23,24,25      | 4,5,6,7,8             |

| 5        |            | 4        | 26,27,28,29,30      | 9,10,11,12,13         |

| 6        |            | 4        | 31,32               | 14,15                 |

| 6        |            | 5        | 33,34,35            | 0,1,2                 |

| 7        |            | 5        | 36,37,38,39,40      | 3,4,5,6,7             |

| 8        |            | 5        | 41,42,43,44,45      | 8,9,10,11,12          |

| 9        |            | 5        | 46,47,48            | 13,14,15              |

| 9        |            | 6        | 49,50               | 0,1                   |

| 10       |            | 6        | 51,52,53,54,55      | 2,3,4,5,6             |

| 11       |            | 6        | 56,57,58,59,60      | 7,8,9,10,11           |

| 12       |            | 6        | 61,62,63,64         | 12,13,14,15           |

| 12       |            | 7        | 65                  | 0                     |

| 13       |            | 7        | 66,67,68,69,70      | 1,2,3,4,5             |

| 14       |            | 7        | 71,72,73,74,75      | 6,7,8,9,10            |

| 15       |            | 7        | 76,77,78,79,80      | 11,12,13,14,15        |

| 16       |            | 8        | 81,82,83,84,85      | 0,1,2,3,4             |

| 17       |            | 8        | 86,87,88,89,90      | 5.6.7.8.9             |

| 18       |            | 8        | 91,92,93,94,95      | 10,11,12,13,14        |

| 19       |            | 8        | 96                  | 15                    |

| 19       |            | 9        | 97,98,99,100        | 0,1,2,3               |

| 20       |            | 9        | 101,102,103,104,105 | 4,5,6,7,8             |

| 21       |            | 9        | 106,107,108,109,110 | 9,10,11,12,13         |

| 22       |            | 9        | 111,112             | 14,15                 |

| 22       |            | 10       | 113,114,115         | 0,1,2                 |

| 23       |            | 10       | 116,117,118,119,120 | 3,4,5,6,7             |

| 24       |            |          | Undefined           |                       |

| 25       |            |          | Undefined           |                       |

| 26       |            |          | Undefined           |                       |

| 27       |            |          | Undefined           |                       |

| 28       |            |          | Undefined           |                       |

| 29       |            |          | Undefined           |                       |

| 30       |            |          | Undefined           |                       |

| 31       |            |          | Undefined           |                       |

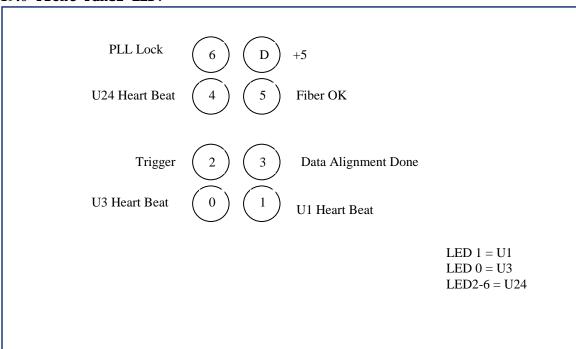

19.0 Front Panel LED:

Trig Monitor Lemo Connector is OR of 30 bits Output OF Hit Coincident Window

| <u>20.0</u> | Front Panel LVDS IN, LVDS OUT:                                                                       |

|-------------|------------------------------------------------------------------------------------------------------|

| 20.0        | LVDS IN  + -  O O 1  O O  O O                                                                        |

|             | 00<br>00<br>00<br>00<br>00<br>00 8<br>P N                                                            |

|             | LVDS OUT  + - Trig Out = MicroScope or HodoScope Coincident O O Hit Bits O O O O O O O O O O O O O O |

|             | P N                                                                                                  |

### 21.0 Appendix A:

Notes:

- Block Erase is used because Chip Erase Command is currently not supported by the IC AT45DB642

- Buffer To Memory Page Program without Built-in Erase is used because with Built-in Erase does not seems to work reliable.

- It takes 3199 pages of AT45DB642 memory to hold config. Data for FX70T. It takes 13 minutes presently to do this.