## **Test Stand Status – Initial Testing**

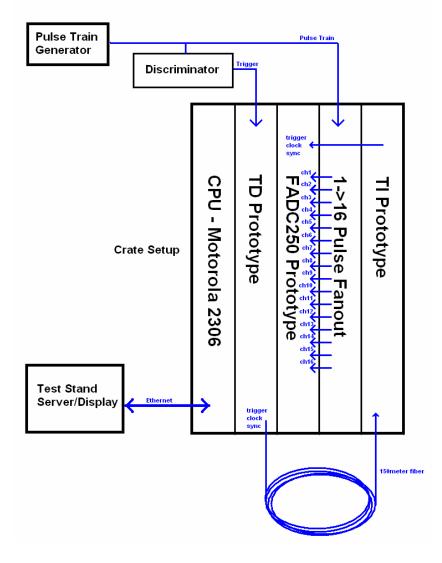

**Test Stand Configuration**

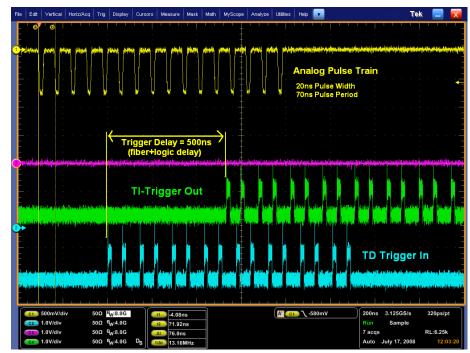

- Used TD, TI Fiber Based Clock & Trig Distribution

- Pulse Train Length of 16, 70ns spaced triggers

- Fed into all 16 FADC250 Channels

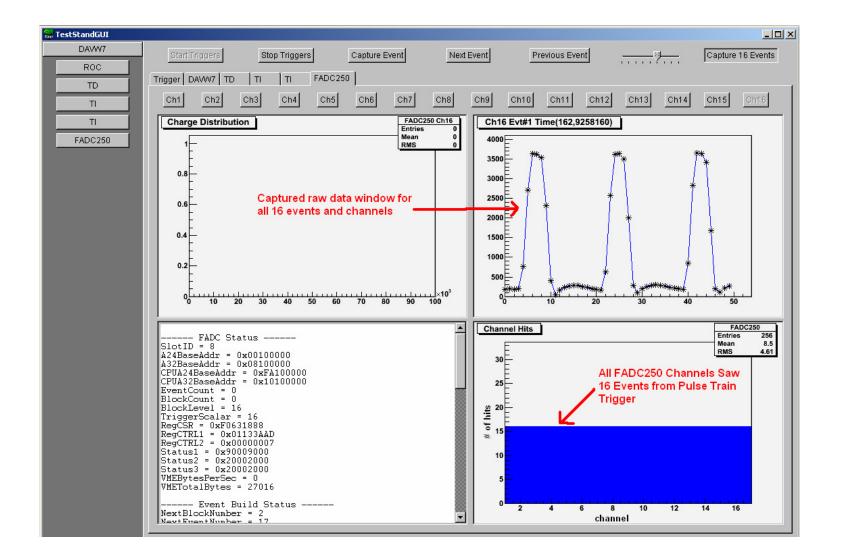

## Test Stand GUI FADC250 Tab Display – Pulse Train Event Capture

## **Test Stand Status Summary/To-do**

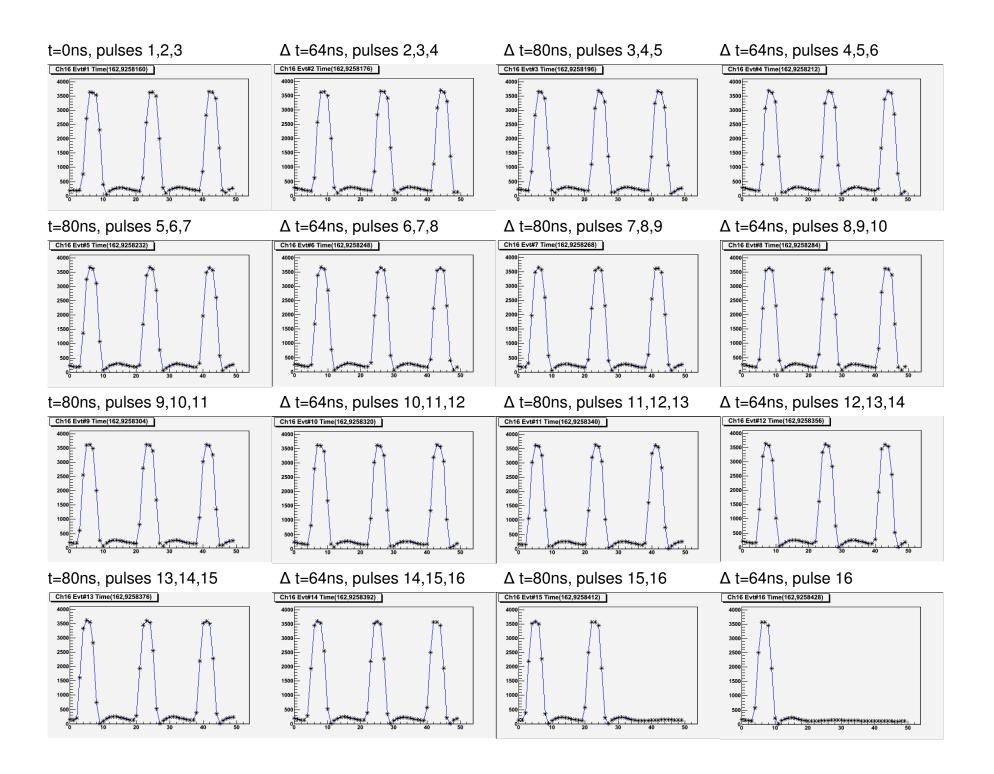

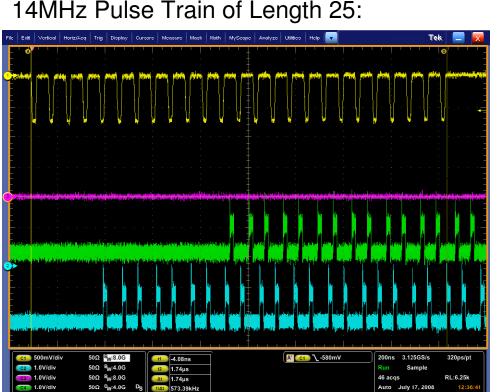

• FADC250 captures this type of pulse train having up to 25 sequential pulses 70ns apart – after this point a bug causes FADC250 to fail - ultimately a BUSY flag will halt the Trigger Supervisor from distributing anymore triggers to prevent overburdening the FADC250.

• This test indicates that the FADC250 pulse processing will easily be able to handle a 200kHz trigger rate.

• Large signal jitter (seen as 16ns in previous capture) is introduced from trigger distribution. The Trigger Supervisor will remove this by storing to the event stream the precise 250MHz clock cycle a trigger happens.