### FADC timing resolution

- Prototype built at IU

- 250 MH sampling (4 ns)

- 8-bit resolution

- saturates at 1.3 V

- clock not synchronized to external source

- User controls

- number of samples to extract from the ring-buffer

- trigger threshold

- trigger offset

- Basic idea

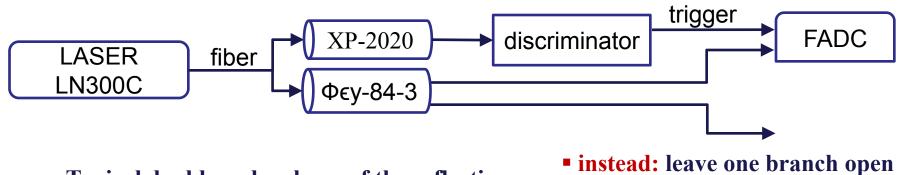

- use laser light and FEU-84-3 PMT to send a signal to the FADC

- apply algorithm described in GlueX-doc-426 that utilize maximumsample time and two preceding times to estimate 50% crossing time

# Algorithm description

assuming Gaussian shape of the raising edge of the pulse one can use two samples preceding the maximum sample to estimate the 50% of peak crossing time

40

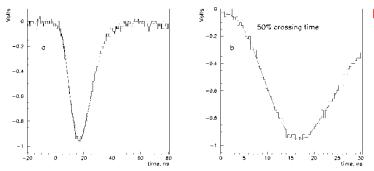

Typical PMT pulse

Digitized pulse to mimic FADC response

polynomial fit to determine 50% of peak crossing time

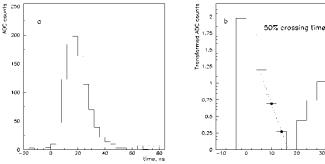

transformation to turn a Gaussian edge into a straight line:

$$aT_i + b = \sqrt{-\ln\left(\frac{S_i}{S_{\text{max}}}\right)}$$

□ two samples needed to obtain *a* and *b*

$$aT_{50} + b = \sqrt{-\ln\left(\frac{1}{2}\right)}$$

comparison between fit and method yielded 150 *ps* resolution for 1.5 V signal

### FADC timing resolution setup

using time difference between two cards to extract the intrinsic resolution of the algorithm not feasible:

±16 ns uncertainty (FADC outputs 4 bytes at the time)

- to produce reflected signal

- advantage: samples always aligned to the same bit

- opportunity: examine sensitivity of the algorithm to the sample arrival time by changing the length of the open end

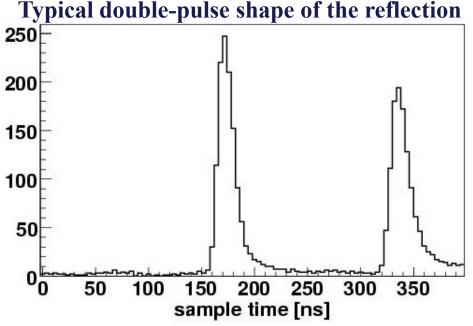

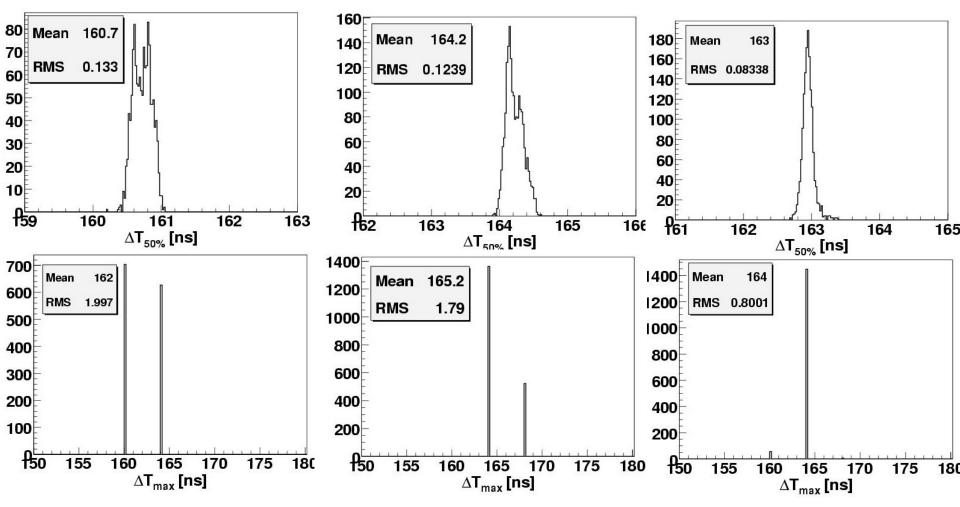

#### Difference in 50% peak crossing time

the timing info depends strongly on maximum sample

what would be the resolution if signals' maxima are always sampled at the same time?

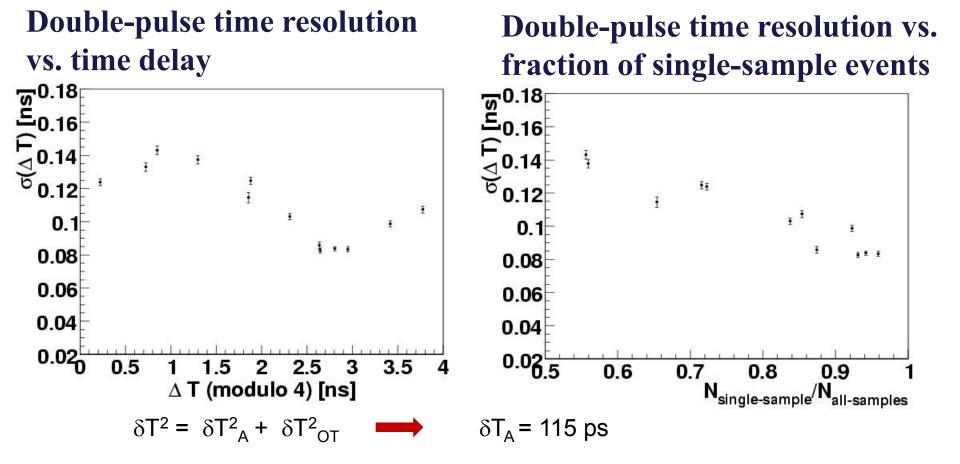

# Single-channel time resolution

A – algorithm OT- other factors (delay variations, PMT transition times)