## **Talk Overview**

- **1. CAEN V1495 VME Module Overview**

- 2. Example of completed V1495 projects at JLAB

- **3. Design tools/resources**

- 4. Example V1495 project walkthrough

# **1.0 V1495 Overview**

### Input/Output Interfaces

- 64 dedicated differential inputs (LVDS, NECL, PECL)

- 32 dedicated outputs (LVDS)

- 2 bidirectional NIM ports

- 3 optional daughter card module slots

### **Daughter Card Modules**

- A395D: 8 bidirectional NIM/TTL ports

- A395A: 32 differential inputs (LVDS, NECL, PECL)

- A395C: 32 ECL outputs

- A395B: 32 LVDS outputs

- A395E: 8 channel 16bit DAC (low speed)

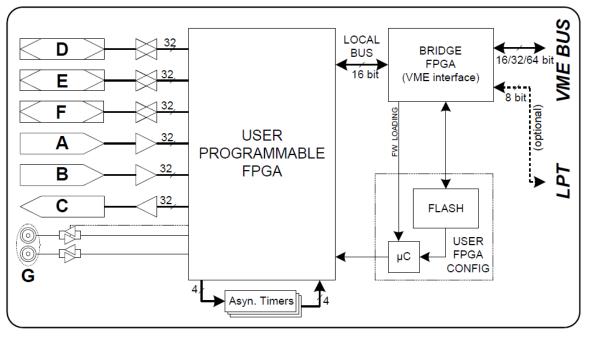

# 1.1 V1495 Block Diagram

### User programmable FPGA

- Custom user logic to interface all front-panel inputs/outputs

- VME bus has access to user logic (for parameter setup, status, event readout)

- VME interface provides 16/32bit single cycle accesses and supports only BLT32 for high speed readout

- FPGA firmware can be updated by user over the VME bus

- Onboard programmable delays for asynchronous delays

## **1.2 V1495 FPGA Resources**

### Altera FPGA: EP1C4F400C6

**General features:**

- 1. FPGA Block RAM: 294912 bits

- Event buffering

- Large delay lines

- Histograms

- 2. PLLs (2)

- Fast I/O sample rates (~200MHz)

- Fast internal sequential logic (up to ~400MHz)

- Synchronize multiple V1495 modules

- 3. Logic Elements (LE): 20,060

- Counters, prescalers, small delay lines

- Lookup tables

- Combinatorial/sequential logic

- Each LE contains a register/latch and 4 input LUT

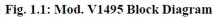

### 1.3 V1495 FPGA LE

- The LE is the basic resource that most high level logic will be synthesized to use

- Software synthesizers will take high level code (state machines, counters, arithmetic operators, logic) and reduce them to utilitize the specific FPGA features

- The synthesizer is very good in general, but in some cases it needs help and can require user to understand the FPGA structure for high speed or density logic to work on the FPGA

## 2.0 V1495 Projects at JLAB

### Hall B IC/Hodoscope Cluster Finder - Ben

Discriminator based 3x3 window calorimeter cluster finding. (424 channels + 72 hodoscope)

#### Hall B Trigger - Ben

Hall B has been using the v1495 as the main trigger processor for the past few years. (sector/global trigger logic)

#### Hall A Signal Fanout – Ben

FastBus ADC and TDC testing board. Provided programmable delays and widths on many maskable ECL channels.

#### Hall C Compton Polarimeter (self-trigger, event readout) – Amrendra Nayaran

1-dimensional, multi-plane cluster finding for a diamond multi-strip detector.

### Hall C GEM Readout– Ben (eventually someone in QWEAK took this project over) Provided triggered readout and buffering for 12 VFAT chips per V1495.

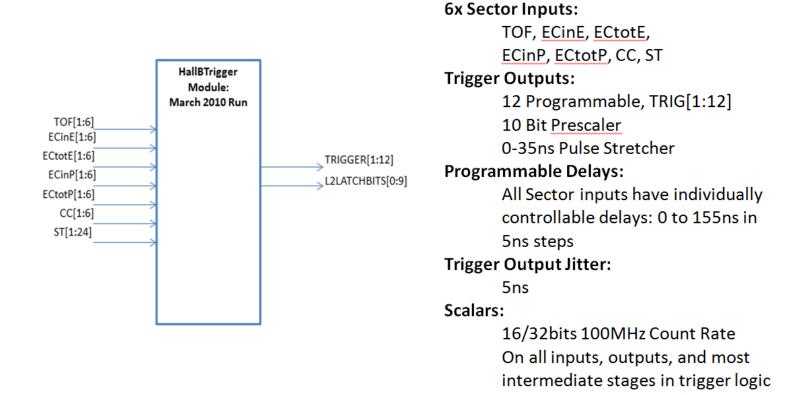

# 2.1 Hall B Main Trigger

HallB Trigger Module – Run March 2010 Description

Implemented on CAEN V1495 Programmable VME Module

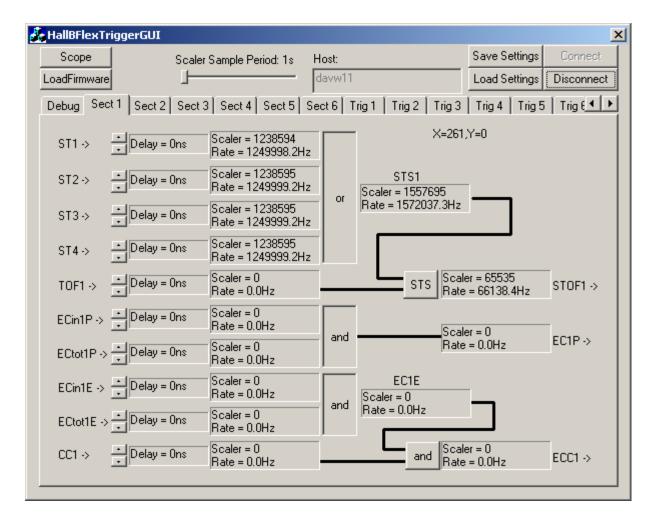

### 2.2 Hall B Main Trigger (sector triggers)

## 2.3 Hall B Main Trigger (global triggers)

| 🛃 HallBFlex Trigger GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ×                                                            |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|--|--|

| Scope     Scaler Sample Period: 1s     Host:       LoadFirmware     davw11                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Save Settings     Connect       Load Settings     Disconnect |  |  |  |  |  |  |  |

| Debug     Sect 1     Sect 2     Sect 3     Sect 4     Sect 5     Sect 6     Trig 1     Trig 2     Trig 3     Trig 4     Trig 5     Trig 6     Image: Sect 7       STOF[1-6] ->     ECP LUT 12:1     or     Scaler = 0     X=449,Y=13     X=449,Y=13       STOF[1-6] ->     ECC LUT 12:1     or     Scaler = 0     Rate = 0.000Hz     and     Scaler = 0       BCC[1-6] ->     FILE: test_tof1.lut     or     Rate = 0.000Hz     and     Scaler = 0       MORA_DLY ->     1     Image: Scaler = 0     Image: Scaler = 0     Scaler = 0     Scaler = 0 |                                                              |  |  |  |  |  |  |  |

| ST_MULT ->MOR<br>Persist = Ons Scaler = 0<br>Rate = 0.000Hz Prescale = 1 Scaler = 0<br>Rate = 0.000Hz > TRIG1                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                              |  |  |  |  |  |  |  |

| MORA -> Delay = Ons Scaler = 0<br>Rate = 0.000Hz -> MORA_DLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | > ST_MULT<br>icaler = 0<br>Rate = 0.000Hz                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                              |  |  |  |  |  |  |  |

### 2.4 Hall B Main Trigger (debug scope)

| Dialog |      |        |                     |               |                |                     | 2    |

|--------|------|--------|---------------------|---------------|----------------|---------------------|------|

|        |      | ı 🔽 Ir | nfinite Persistence | Clear Display | Continuous Tri | gger Single Trigger | Stop |

| Signal | Trig | Cursor |                     | <u></u>       |                | r = 95ns            |      |

| CCS    | x    | 1      |                     |               |                |                     |      |

| CC6    | x    | 1      |                     |               |                |                     |      |

| MORA   | x    | 0      |                     |               |                |                     |      |

| MORB   | X    | 0      |                     |               |                |                     |      |

| STOF1  | X    | 1      |                     |               |                |                     |      |

| STOF2  | X    | 0      |                     |               |                |                     |      |

| STOF3  | X    | 0      |                     |               |                |                     |      |

| STOF4  | x    | 0      |                     |               |                |                     |      |

| STOF5  | X    | 0      |                     |               |                |                     |      |

| STOF6  | X    | 0      |                     |               |                |                     |      |

| ECP1   | X    | 1      |                     |               |                |                     |      |

| ECP2   | X    | 1      |                     |               |                |                     |      |

| ECP3   | X    | 1      |                     |               |                |                     |      |

| ECP4   | Х    | 1      |                     |               |                |                     |      |

| ECP5   | Х    | 1      |                     |               |                |                     |      |

| ECP6   | X    | 1      |                     |               |                |                     |      |

| ECC1   | X    | 1      |                     |               |                |                     |      |

| ECC2   | X    | 0      |                     |               |                |                     |      |

| ECC3   | Х    | 0      |                     |               |                |                     |      |

| ECC4   | X    | 0      |                     |               |                |                     |      |

| ECCS   | х    | 0      |                     |               |                |                     |      |

| ECC6   | х    | 0      |                     |               |                |                     |      |

| STMULT | X    | 1      |                     |               |                |                     |      |

| TRIG1  | 1    | 1      |                     |               |                |                     |      |

| TRIG2  | х    | 0      |                     |               |                |                     |      |

| TRIG3  | X    | 0      |                     |               |                |                     | -    |

| TRIG4  | х    | 0      |                     |               |                |                     |      |

| TRIGS  | X    | 0      |                     |               |                |                     |      |

| TRIG6  | X    | 0      |                     |               |                |                     |      |

| TRIG7  | X    | 1      |                     |               |                |                     |      |

| TRIG8  | X    | 0      |                     |               |                |                     |      |

| TRIG9  | X    | 0      |                     |               |                |                     |      |

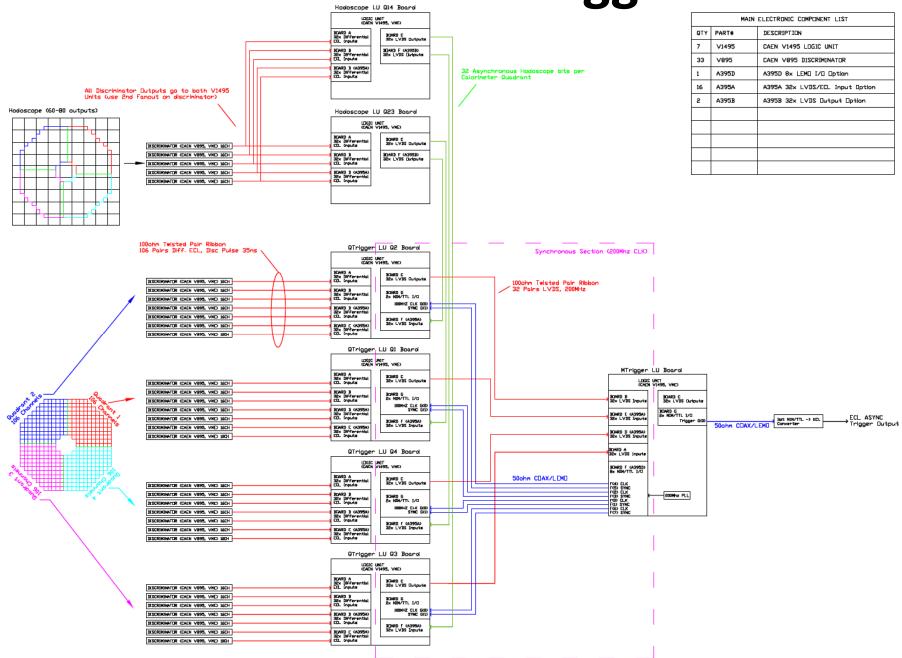

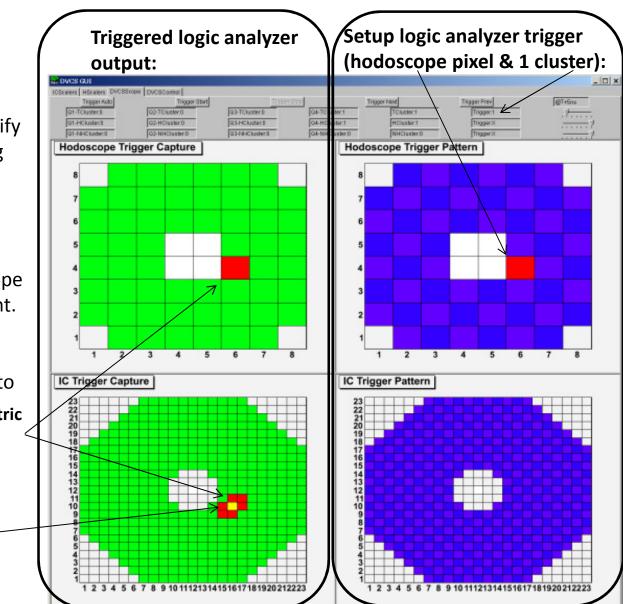

## 2.5 Hall B IC Trigger

# 2.6 Hall B IC Trigger

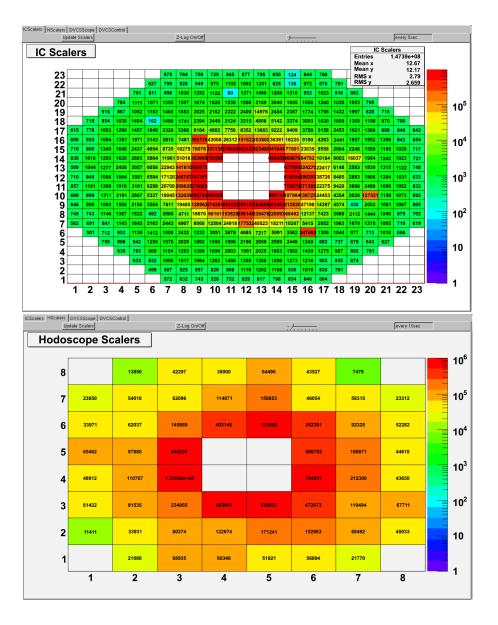

### Embedded logic analyzer was developed for the 424 Channel Inner Calorimeter / 72 Channel Hodoscope in Hall B

• Cluster finding trigger implemented in multiple V1495 CAEN logic units. Scalers for all 496 channels & logic analyzer also embedded in trigger hardware.

Trigger algorithm looked at all 3x3 window combinations of calorimeter searching for #hit towers to go above threshold to define cluster

• Hodoscope pixels were matched to IC cluster positions to identify charged/neutral clusters and provide counts to global trigger

# 2.7 Hall B IC Trigger

### **2D Logic Analyzer Details:**

- Goal was to provide a remote debug interface to identify bad channels, verify cluster finding algorithm, check timing

- Logic analyzer runs in parallel, nonintrusive, to calorimeter trigger

- Can setup trigger on any IC/Hodoscope pixel arrangement and/or cluster count.

- After trigger, you can move forward/backward in time by ~250ns to see timing details

Geometric

- Not Hit Tower/Pixel Hit Tower/Pixel Cluster Found Don't care trigger

Match

## 3.0 Software & projects to download

**Quartus II Web Edition (FPGA compiler-synthesizer/fitter):**

Link: <u>https://www.altera.com/download/dnl-index.jsp</u> Comments:

- Get version 9.1sp2 or 10.1sp1 (newer versions of free edition don't include support for Cyclone I series FPGA that's on the V1495

- Runs under Linux or Windows

### Modelsim-Altera Starter Edition (FPGA simulation):

Link: <u>https://www.altera.com/download/dnl-index.jsp</u> Comments:

- Get the version that matches the Quartus II Web Edition you have

- Runs under Linux or Windows

### CAEN V1495 Example Projects:

Link: <u>http://www.caen.it/csite/CaenProd.jsp?parent=11&idmod=484</u> Comments:

- Under "Software/Firmware" download all "v1495\*demo\*" files

- Under "Documentation" dowload "V1495 User Manual"

- These are CAEN example Altera Quartus projects for the v1495 that can be used as a basis to develop user specific designs for the v1495

# **3.1 Additional Resources**

Recommended Design Practices (i.e. DO & DONTS for what kind of logic to implement on the FPGA):

http://www.altera.com/literature/hb/qts/qts\_qii51006.pdf

Recommended HDL Coding Styles (i.e. how to write code to ensure the synthesizer can understand what you want):

http://www.altera.com/literature/hb/qts/qts\_qii51007.pdf

VxWorks VME based firmware updater for 1495 (Intel version to come when needed)

Contact: <u>braydo@jlab.org</u> or <u>boiarino@jlab.org</u>

### USB Blaster quick programming & debug tool:

- If think you'll be developing for the v1495, this tool pays for itself and more

- Get the generic one from Digikey (Digikey Part# P0302-ND) for \$75

- This allows use of SignalTap for debugging your code while it runs in the board a very powerful logic analyzer for debugging

# 4.0 Example Design Walkthrough

### General Design Steps...

- 1) Breakdown the design into small modules (e.g. scalers, prescalers, delay line, memory, state machine, simple combinatorial logic, etc...)

- 2) Implement each module as a small, single entity (either VHDL, Verilog, Schematic)

- 3) Test each module using a dedicated testbench for each module that simulates (using Modelsim for example) as many features as possible (preferably all)

- 4) Build partial/full design out of these smaller modules and write a testbench to simulate this larger piece...

- 5) Once full design simulation is complete, compile (using Altera Quartus). Resolve timing/fitting problems (re-simulate any modified code)

- 6) Load compiled design into v1495 and test with real signals (can use SignalTap for debugging if needed)

Modified files: Coin\_reference.vhd,

V1495usr\_pkg.vhd

- -- B.R. modified (start)

- -- B.R. modified (end)

Added files: Scaler.vhd, DigitalDelayLine.vhd, PLLBlock.vhd, TriggerTestBit.vhd

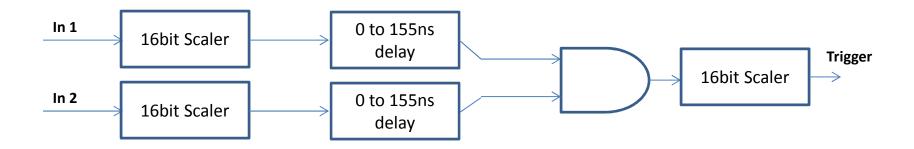

# 4.1 Example Design

### **Example design:**

- Form coincidence trigger signal from 2 inputs with unknown skew.

- Scalers on inputs and output signal

- Programmable delays on input signals to form coincidence by changing VME registers

- 200MHz clock sets sample rate, delay step size, and maximum scaler rates (200MHz/2)

# **4.2 Example Design**

Starting from CAEN Coincidence Altera Quartus Project example:

V1495\_User\_Demo\_QuartusII\_Project\_2\_0-624.zip

I added the following files to the project:

| Scaler.vhd            | programmable scaler     |

|-----------------------|-------------------------|

| DigitalDelayLine.vhd  | programmable delay line |

| PLLBlock.vhd          | 200MHz PLL              |

| TriggerTestBit.vhd    | Example design          |

| coin_reference_tb.vhd | Overall design testbech |

|                       |                         |

I modified the following files: V1495usr pkg.vhd

coin reference.vhd

Added new register addresses Dropped in TriggerTestBit entity here, and update VME registes

...I put the following comments around the sections of the orignal CAEN project files that I modified:

- -- B.R. modified (start)

- -- B.R. modified (end)